主题中讨论的其他器件: LMK04832

您好!

我们希望将 LMK04828 CLK 合成器用于 RFSoC FPGA、以实现多板同步(ADC/DAC 采样)

以下是规格

1] ADC 采样率= 1350Mhz

2] DAC 采样率= 5400MHz

我们将遵循"同步方法:ZDM"并遵循以下规则

因此、请验证我的多板同步时钟方案

考虑到规则

ADC/DAC CLK = 337.5MHz

SYSREF = 5.625MHz

I/P REF FREQ = 5.6225MHz

请验证相同

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们希望将 LMK04828 CLK 合成器用于 RFSoC FPGA、以实现多板同步(ADC/DAC 采样)

以下是规格

1] ADC 采样率= 1350Mhz

2] DAC 采样率= 5400MHz

我们将遵循"同步方法:ZDM"并遵循以下规则

因此、请验证我的多板同步时钟方案

考虑到规则

ADC/DAC CLK = 337.5MHz

SYSREF = 5.625MHz

I/P REF FREQ = 5.6225MHz

请验证相同

您好、Shekhar、

这种方法通常看起来不错。 以下是一些注释。

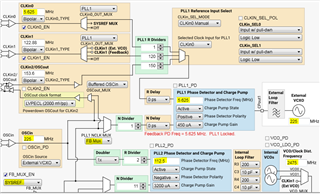

(1)如果您使用 LMK04832、则160MHz VCXO 可以在 PLL2的320MHz 相位检测器频率下运行(160MHz 加倍)、而 LMK04828的频率为80MHz (最大 PDF 为155MHz)。 这将为您提供性能提升。

(2)您将 Dout8显示为337.5MHz、将 SDout3显示为5.625MHz。 我建议为您的器件时钟和 SYSREF 使用偶数对。 例如、Dout8 = 337.5MHz 和 SDout9 = 5.625MHz 或 Dout2 = 337.5MHz 和 SDout3 = 5.625。

(3)这是您实施过程中的最大细节。 与您指定的条件#1和#2 (在这种情况下、您也将有#4)相关。 您是否计划使用脉冲 SYSREF 或连续 SYSREF? (3A)如果使用连续 SYSREF、则 SYSREF 相位将对齐。 由于存在串扰问题、我们不建议始终保持连续运行、如果将其关闭、您可以节省功耗。 但是、这是一种有效的技术、可以在短时间内连续运行、同步 JESD204B 接收器-通常是...

-打开连续 SYSREF

-等待交流耦合 SYSREF 稳定

-告知 JESD204B 接收器停止侦听 SYSREF,同时满足所有接收器的 SYSREF 频率的设置和保持时间。

-然后关闭连续 SYSREF。

(3B)如果您使用脉冲 SYSREF、则从 LMK04828到接收器的物理接口最好是直流耦合、您必须同时从两个 LMK04828器件请求 SYSREF、以使 SYSREF 输出对齐。 否则,它们可能在 n*SYSREF 周期前关闭。 (这对于常规 JESD204B 同步是可以接受的)。 有几种方法可以生成 SYSREF 脉冲:

(i)使用 SYSREF 脉冲发生器模式并通过满足 PLL1基准设置和保持时间的软件请求 SYSREF 脉冲。

(ii)使用 SYSREF 脉冲发生器模式并通过 SYNC 引脚请求 SYSREF 脉冲、满足 PLL1基准的设置和保持时间。

(iii)使用 SYSREF 重定时模式(SYSREF_MUX 选择 D 触发器输入)、并在 SYNC 引脚上提供 SYSREF/SYNC 输入、以满足 PLL1基准的设置和保持时间。

(IV)使用 SYSREF 重新计时模式(SYSREF_MUX 选择 D 触发器输入)、并在 CLKin0上提供 SYSREF/SYNC 输入、以满足 PLL1基准的设置和保持时间。

请注意、根据 JESD204B 规范、它不需要在 JESD204B 接收器的同时具有 SYSREF。 只有 LMFC 时钟周期的时间模量是相同的。 这意味着您无需担心任何设置和保持时间。 LMK04828将负责提供 SYSREF、无论您何时提出请求。

-我对您的设计条件的解释表明您确实期望这种一致性,因此必须考虑到设置和时间。

(4)您需要决定用于5.625MHz 输入的时钟输入。 我建议保留 CLKin0可用、以便您可以将其用于 SYSREF/SYNC 相关输入函数。 通常、我建议将您的5.625MHz 输入连接到 CLKin1或 CLKin2、而不是 CLKin0。

--

以下两条建议可能有助于您同时从两个器件生成 SYSREF 脉冲。

最简单的解决方案是让 LMK04832生成每个器件的 CLKin1的5.625MHz 基准(LMK04832在每个器件的时钟输出上都有大分频器)、然后提供一个5.625MHz SYSREF 信号、该信号进入每个器件的 CLKin0。 这是上面的方法3b、iv。 在 LMK04832上、您可以为每个 LMK04828 (或 LMK04832)调整 SYSREF 上的时序、然后将 SYSREF 重新计时到 JESD204B 目标。

-然后使用 LMK04832上的 SYSREF 脉冲发生器功能将 SYSREF 脉冲发送到下游器件。

第二种选择是让 LMK04828之一为下一个板或 N 个其他板生成 SYSREF 输出。 将这个 sysref 输出连接到 CLKin0、时序可相对于5.625MHz 基准进行调整。

-然后使用上游 LMK04828上的 SYSREF 脉冲发生器功能将 SYSREF 脉冲启动到其自己的 JESD204B 目标和下游 LMK04828、后者将重新计时并输出 SYSREF。 这样做的问题可能是 PIPLELINE 延迟会很大、从而使您在 SYSREF 的放置方面具有很大的灵活性、从而确保所有 JESD204B 在完全相同的时间接收 SYSREF。 但它是确定性的。 借助 LMK0482x (与 LMK04832相比)、可以通过使用 SYSREF_CLKin0_MUX 绕过基于 CLKin0的一些初始电路来降低流水线延迟。 LMK0482x 和 LMK04832都允许您同时绕过 SYSREF 数字延迟。 借助 LMK0482x、我发现两个器件可以同时实现 SYSREF 输出。 至少在某些条件下。

73、

Timothy

您好、Timothy、

感谢您的回复、我将考虑 为您的器件时钟和 SYSREF 使用偶数对。

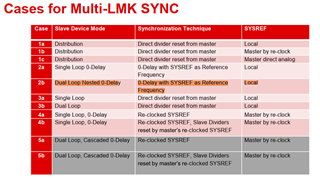

我们将遵循以下方法进行多 LMK 同步(2b)、参考频率= Sysref 频率

同步方法也可作为零延迟模式、在满足 ZDM 规则的情况下、我不需要为两个器件同时发生脉冲 SYSREF、而是使用具有低频率到 PLL1的双环路模式

经过上述考虑后,我的计划是否可以?

注意:我不想使用任何主器件/根器件 LMK、也没有将 SYNC/CLKIN0用于同步目的的计划/方案/选项。

您好、Timothy、

修改的要求

1] DCLK = 112.5MHz (使用内部 RFSoC PLL 获得1350Mhz)

2] SDCLK = 5.625MHz (采样 CLK/16的整数倍、即1350/16 = 84.375)

为此、我们将在 TICS Pro 中使用以下设置

请验证方案并建议更改(如果有)...

谢谢

Shekhar

您好、Shekhar、

您是否/是否能够在电路板和系统上测试此项、以确定其是否满足您的要求? 在一天结束时、您需要确认所有需要的性能、等等 例如、由于在连续模式下运行 SYSREF 而可能产生的任何杂散。 观察 DCLKoutX 和 SDCLKoutY 之间是否没有分离。

[引用 userid="175031" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/998864/lmk04828-multi-board-lmk-sync/3695414 #3695414"] 外部 VCO 被选为225MHz[/quot]我想您是说外部 VCXO 频率选择为225MHz。 只要您对性能感到满意、实际上它是一个外部 VCO 就可以了。

[引用 userid="175031" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/998864/lmk04828-multi-board-lmk-sync/3695414 #3695414"]内部 VCXO 应在(2370 - 2630) MHz 或(2920 - 3080MHz) MHz[/引用]范围内我们在内部有 VCO。

[引用 userid="175031" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/998864/lmk04828-multi-board-lmk-sync/3695414 #3695414"]只能通过内部 VCXO 分频器生成 DCLK 频率,SDCLK 频率可以作为 SYSREF 频率生成[/quot]没有内部 VCXO 分频器。 您可能是指 VCO 的通道分频器? 在此配置中、器件时钟和 SYSREF 均由 VCO 的分频器生成。 这是可以的。

[引用 userid="175031" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/998864/lmk04828-multi-board-lmk-sync/3695414 #3695414"]由于 我们需要的 SYS_REF 与生成的 SYS_REF 相同、因此它不需要通过任何分频器、因此可以选择如图所示的 SYSREF 时钟输出。 [/报价]所有内容均已正确选择。 但是、SYSREF 由 VCO 的 SYSREF 分频器产生。

73、

Timothy

一般而言,只要您不需要 CLKin0 --> CLKout,或者同时需要使用两个级联器件的 SYSREF,我建议使用 LMK04832。

[引用 userid="175031" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/998864/lmk04828-multi-board-lmk-sync/3698218 #3698218"]我们能否继续使用上述用于 PLL1和 PLL2的相位检测器频率设置[/引用]LMK04832允许您以320MHz 的频率运行 PLL2。 PLL1仍需要更低的5.625MHz (或更低)。 但这不是问题、因为 VCXO 将执行抖动消除。

73、

Timothy

您好、Timothy、

在其中一个类似的项目中、我们需要我们的输出时钟彼此同相、但不需要处于 w.r.t 输入参考时钟相位。

那么、我们是否可以忽略 ZDM 的第一个规则、即 I/P CLK = GCD (O/P CLK、I/P CLK)、并且只遵循第二个规则、即在 ZDM 嵌套拓扑中作为 SYSREF 反馈的最低 o/p 频率?

这样、我们将获得确定性相位 w.r.t I/P

您好、Shekhar、

由于 Timothy 是 ooo、我可以回答。 为简单起见、假设输入参考时钟是 SYSREF 频率的两倍。 由于 R 分频、每个 LMK 输入相位检测器都有两个可能的相位、并且由于 SYSREF 与该相位检测器对齐、因此也可能有两个 SYSREF 相位。 即使您重置 SYSREF 分频器相位、但不知道每个器件上的 R 分频器相位、也无法保证每个器件上的输出相位相同。

实际上、LMK04832能够复位 R 分频器(LMK0482x 不能复位)。 因此、从技术上讲、可以在每个器件上手动设置 R 分频器相位、从而使 LMK04832忽略 ZDM 的第一条规则。 要同步每个器件、首先会同时复位所有 R 分频器。 然后可以生成同步事件、 只要同步事件很快速(几 ns)、以至于在分频器再次开始分频后不可能出现周期滑动、每个输出都将同相、并且每个输出只有一个可能的相位。 只有当输入时钟是 SYSREF 的倍数时、才会出现这种情况、因为无法专门复位 N 分频器。

如果 SYSREF 频率不是相位检测器频率(即、输入相位检测器的 N 分频器不是1)、则在输入到输出同步中不再能使用任何 ZDM 规则。 在这种情况下、必须在每个器件上的同一 VCO 周期内手动同步输出分频器-不可避免地需要 CLKin0同步、动态数字延迟或其他补偿机制。

此致、

Derek Payne

尊敬的 Derek:

感谢您的解释。

实际上、我忘了提到我上面提到的另一个类似项目只有1个 LMK04828。

在这种情况下、我需要在任何加电时间、LMK 的 O/P 处于同相状态、而不是与 I/P 基准时钟同相。

(因为、正如您提到的、SYSREF 可以采用任何相位、但由于我有一个器件、因此可以确保 SYSREF 一次可以位于其中一个相位)

如果我的系统/项目有多个 LMK,那么所有 ZDM 规则都必须而且应该被注意。

如果我错了、请改正。

您好、Shekhar、

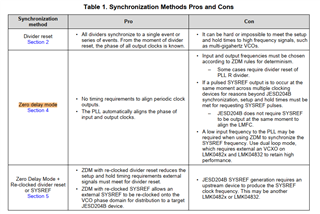

对器件进行编程时、分频器状态实际上是随机的。 零延迟规则并不能保证任何器件时钟与同一器件上的 SYSREF 之间的相位对齐-它只是保证了在具有相同输入时钟相位的多个器件上运行的 SYSREF 之间的关系。 在反馈路径中将 ZDM 配置与 SYSREF 结合使用的主要好处是 SYSREF 还可以将同步脉冲重定时到精确的 VCO 时钟周期、而无需用户进行任何复杂的计时。 通过切换 SYNC_POL 位或使用 SYNC_PLLx_DLD 位触发锁定检测的同步关闭、甚至可以完全在软件中生成此同步。 但是、无论怎样、输出分频器都需要通过相位同步来建立它们的相位关系。 对于多器件方案也是如此。

在多器件方案中遵循 ZDM 规则的好处是:

如果您只有一个器件、并且该器件不需要具有可重现的输入到输出相位关系、那么您不必遵循 ZDM 规则来实现可重现相位关系。 您只需引入一个任意定时的软件同步、并通过这种方式设置器件时钟/SYSREF 相位关系。 ZDM 规则的主要优势在于、它们通过满足在低 MHz 范围内运行的 SYSREF 时钟的设置/保持时间、而不是在 GHz 范围内运行的 VCO、建立了一种在多个器件上生成等时同步事件的可靠方法。 当您需要的只是使单个器件上的所有输出具有可重现的相位关系时、ZDM 是多余的-只需同步即可设置相位关系、这样就可以完成。

这有道理吗?

此致、

Derek Payne

尊敬的 Derek

因此、我们将只通过软件切换"SYNC_POP"位、并期望 SDCLK 和 DCLK 同相、而与 I/P 参考 CLK 无关。

我将 SYNC 或 CLKIN0引脚保留为"无连接"。

因此、对于以下的 REQ

1) 1) SYSREF = 5.625MHz

2) 2) DCLK = 112.5MHz

这两个 CLK 输出都需要同相

我使用以下配置

CLKIN1 = 5MHz

PDF1 = 0.625MHz

VCXO = 225MHz

PDF1 = 112.5MHz

VCO0 = 2475MHz

FB_MUX = SYSREF_DIV

PLL1 N CLK MUX = FB_MUX

Shekhar、

这对我来说很好。

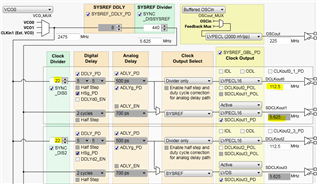

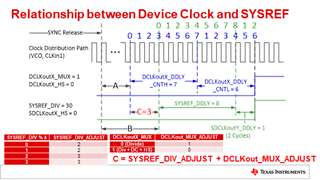

我在下面附加了一张幻灯片图像、这有助于为每个输出时钟和 SYSREF 配置数字延迟、以确保根据需要对齐。 您可以使用此幻灯片图像及其包含的公式和表格、根据所需的 SYSREF_DIV 和 DCLKoutX_CNTL、SYSREF_DDLY 和 SDCLKoutY_DDLY 值计算所需的 DCLKoutX_DDLY、DCLKoutX_MUX。

在本例中、SYSREF_DIV = 440、DCLKoutX_DIV = 22、因此不需要 DCC + HS。 因此、SYSREF_DIV_ADJUST = 2、DCLKout_MUX_ADJUS=1、且 C = 3。

对齐器件时钟和 SYSREF 的有效组合为:

[编辑:我最初混乱、请参阅下面的修订值]

DCLKoutX_DDLY_CNTH = 7

DCLKOUTx_DDLY_CNTL = 6

SDCLKoutY_DDLY = 1 (2个周期)

若要对齐 SYSREF_DDLY、使 SYSREF 与器件时钟的上升沿同时:

[编辑:我最初搞错了、请参阅下面的修订公式]

SYSREF_DDLY = DCLKoutX_DDLY_CNTH + DCLKoutX_DDLY_CNTL -(C + SDCLKoutY_DDLY (周期))= 7 + 6 -(3 + 2)= 8

如果您希望与下降沿对齐、由于2475/112.5 = 22、您可以向 SYSREF_DDLY 添加22/2 = 11以强制对齐到下降沿。 新的 SYSREF_DDLY 值应为8 + 11 = 19。 这应该清楚地说明了如何相对于器件时钟相位设置 SYSREF 相位。

此致、

Derek Payne

尊敬的 Derek:

感谢您的详细解释。 我假设我的问题已得到解决。 以下是结论性意见

查询:

Shekhar、

非常全面的总结。 我同意您针对单器件情况总结的所有内容。 对于多器件情况:

DCLK 和 SCLK 的数字延迟决定了 SYNC 事件之后允许的 VCO 周期数、该事件将在时钟开始前被吞没。 在 TICS Pro 中执行"同步分频器"功能将自动保证器件时钟与 SYSREF 对齐是不正确的。 更准确地说:始终存在 DCLK/SCLK 数字延迟和全局 SYSREF 延迟的设置、这些设置可确保器件时钟和 SYSREF 在同步事件后共享一个边沿。 但数字延迟的设置因分频值而异、必须事先计算。 默认数字延迟值通常不正确、因为默认数字延迟值是为默认分频器值选择的。 此外、您并不总是希望器件时钟和 SYSREF 共享边沿;例如、在许多系统中、SYSREF 的设置和保持窗口以器件时钟的下降边沿为中心。

数据表第8.3.5节"将 SYSREF 添加到器件时钟对齐"给出了一个等式、可用于使用 DCLK/SYSREF 分频器值、DCLK 的占空比校正和数字延迟、针对任何给定的器件时钟预先计算 SYSREF 到器件时钟对齐。

此致、

Derek Payne

尊敬的 Derek:

感谢您的解释。

我们有以下疑问

您好、Shekhar、

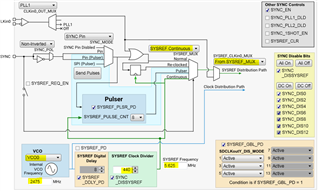

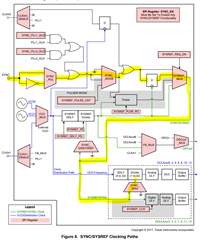

同步路径、假设 SYNC 引脚或 SYNC_POL 切换、使用 SYSREF_MUX =在遵循 ZDM 规则的情况下重定时 SYSREF 分频器:

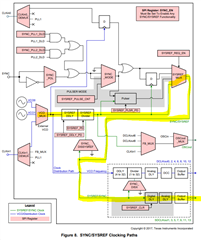

SYSREF 路径、同步完成后、使用 SYSREF_MUX =连续 SYSREF:

此致、

Derek Payne