主题中讨论的其他器件: LMX2820、 LMX2572

尊敬的:

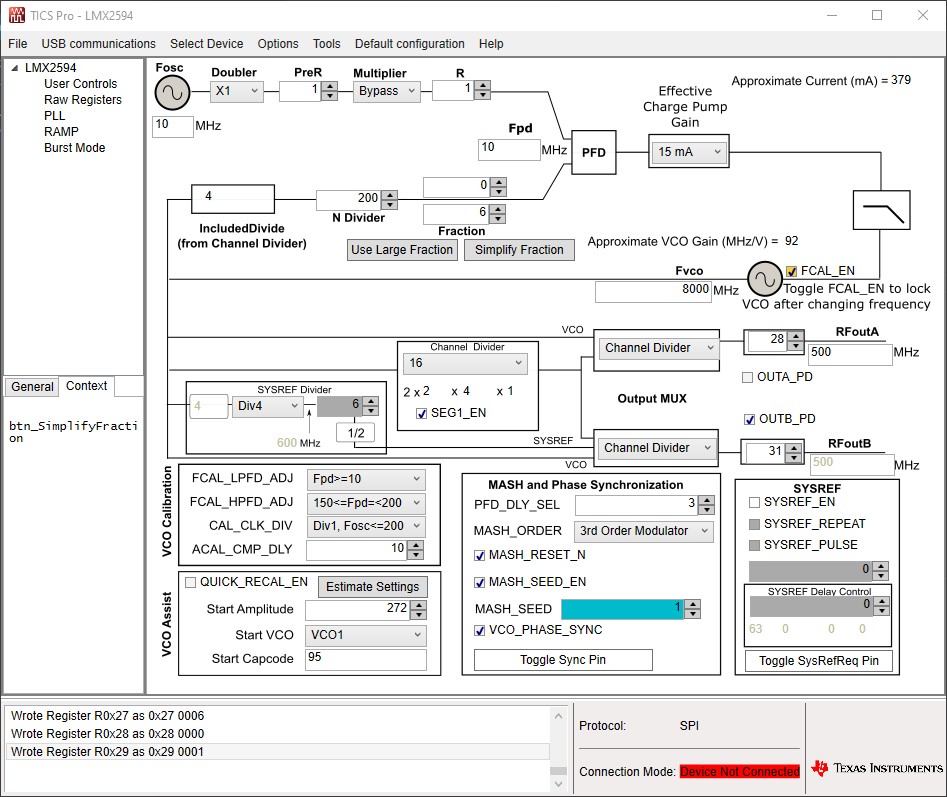

我会对两个 LMX2594之间的相移有疑问。 我有一个定制板和一个定制程序 、用于导入由"TICS Pro"软件生成的寄存器文件。 加载寄存器映射后、仅修改所需的寄存器(当前仅修改 MASK_SEED)。

寄存器加载到两个 LMX 板后、我可以获得相位同步。 由于实际的相移 是随机的、因此在我想对信号进行相移后、问题就会开始

例如、下面是两个电路板的计算值。 在我写入寄存器后、我获得500MHz 的锁定和相位同步。

从配置中、每个 MASK_SEED 步骤应生成 PH=360*4/(6*16)=15度的移位。 如果 我 多次写入相同的值、相位将发生变化。

相移的寄存器按如下方式进行更改:

对寄存器40进行写操作

2.写入寄存器41

3.向寄存器44写入 MASK_RESET_N=0

4. 向寄存器44写入 MASK_RESET_N=1

我错过了什么吗?