您好!

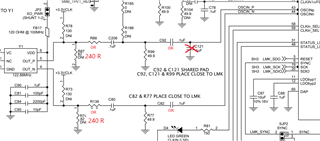

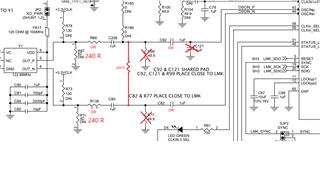

我们使用 的是 DAC3XJ8XEVM 评估板、该评估板默认随附122.28MHz LVCMOS 至 OSCIN。

e2e.ti.com/.../DAC3XJ8XEVM_2D00_SCH_5F00_D.pdf

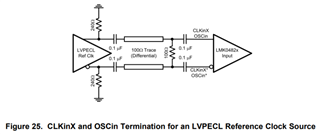

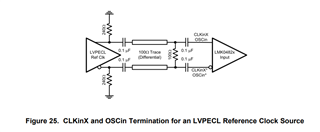

我们将 Y1更改为100MHz LVPECL https://www.crystek.com/crystal/spec-sheets/vcxo/CVPD-922.pdf 、然后将 LVPECL 输入电路更改为 OSC IN 输入

但 PLL2未锁定。

具有 J17 CLKIN1的外部输入时、PLL1处于锁定状态、但 PLL2未锁定

我们缺少了什么...?