Other Parts Discussed in Thread: LMC555, NE555, LM555, NA555, TLC551, SE555, TLC552, TLC555, SA555, CD4060B, CD4024B, CD4020B

器件型号之间有何差异?

如何设置输出频率和占空比?

为什么实际频率与公式 1.44 /[(RA + 2 * RB)* C]不同?

为什么加电后的第一个输出脉冲与后续脉冲不同?

最大频率是多少?

最小频率是多少?

计时器的精度如何?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: LMC555, NE555, LM555, NA555, TLC551, SE555, TLC552, TLC555, SA555, CD4060B, CD4024B, CD4020B

器件型号之间有何差异?

如何设置输出频率和占空比?

为什么实际频率与公式 1.44 /[(RA + 2 * RB)* C]不同?

为什么加电后的第一个输出脉冲与后续脉冲不同?

最大频率是多少?

最小频率是多少?

计时器的精度如何?

此常见问题解答涵盖了 A 稳态电路。 下面的图1显示了使用 LM555、NA555、NE555、SA555和 SE555计时器的 A-stable 电路、这些计时器分别称为 LM、NA、NE、SA 和 SE。 由于其设计、它们被称为双极计时器。 本常见问题解答还涵盖了 LMC555和 TLC555计时器、这些计时器在下文中分别称为 LMC 和 TLC。 作为一个小组、由于其设计、它们被称为 CMOS 计时器。 此常见问题解答也适用于 xx556、TLC551和 TLC552计时器。 计时器的电源电压引脚使用具有相同功能的不同符号 VS、VCC、VDD。

图1. 基本 A 稳态电路

顾名思义、A 稳态模式没有稳定状态。 输出以两个电阻器和一个电容器设定的速率在低电平和高电平之间交替。 A 稳态‘将‘THRESHOLD 引脚’、Trigger 引脚’和计时电容器连接在一起,以便定时器在电容器电压在1/3 VS 和2/3 VS 之间斜升时自行触发。

电阻器(RB)从‘d电容器连接到“电荷引脚”。 这会设置放电时间、其中输出为低电平。 低电平时间为 rb * C * ln (2)。 ‘d电荷引脚’和 VS 之间的电阻器(RA)设定充电时间,此时输出为高电平。 高电平时间为(RA + RB)* C* ln (2)。 充电电流同时流经 RA 和 RB。 周期周期是低电平和高电平时间的总和、(RA + 2 * Rb)* C* ln (2)。 频率等于时间周期的倒数1.44 /[(RA + 2 * Rb)* C]。

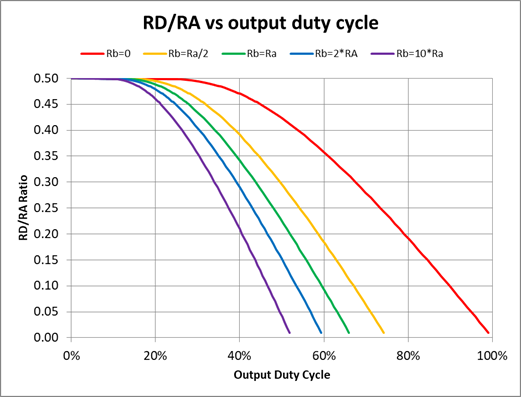

正占空比将是高电平时间除以周期(RA + RB)/(RA + 2 * RB);请注意,公式中没有“C”分量。 换言之、占空比不随电容而变化。 此配置可实现50%至99%之间的正占空比。 RA/RB 比率与占空比之间的关系如图2所示。 RA 的低电阻值将增大计时电阻器使用的电流。 使用外部晶体管或逆变器对输出进行反相是获得小于50%占空比的一种方法。

图2. 正占空比与 RA/RB 电阻器比率

给出的简单时序公式为:1.44 /[(RA + 2 * RB)* C]、未考虑传播延迟。 简单公式中的误差随着 A 稳态频率的升高而增加。 图3中显示的更复杂的公式可用于更准确地计算预期的低电平和高电平时间。 传播延迟直接延长了每个输出状态的结束时间。 传播延迟还会产生更大的电容器摆幅电压、这会增加下一个电容器电压斜升所需的时间。 TPLH 是输出低电平到高电平的延时时间、而 tPHL 是输出高电平到低电平的延时时间。 图3中的图形显示了这些输出传播延迟的影响。

图3. A 稳频公式、包括振荡频率为1/[tc (H)+tc (L)]的传播延迟

简单的50%占空比电路

CMOS 计时器的输出级提供低输出电压和高输出电压、即 VOH 和 VOH。 这些电压在轻负载下接近电源轨。 ‘d,从输出到计时电容器的单个电阻器可以替代使用“电荷引脚”的两个电阻器。 这提供了几乎相等的充电和放电电流。 双极定时器上的 VOH 明显低于正电源轨。 因此输出占空比不会是50%。

计时电容器通过由输出 VOH 和 VOL 电平供电的同一电阻器进行充电和放电。 这会‘d‘ischarge pin’(电荷引脚)作为备用输出。 ‘d将‘ischarge pin’保持悬空。 VOL 驱动比 VOH 驱动强、因此占空比略高于50%。 然而、当 RC >> VOH 驱动器电阻时、50%占空比的变化不大。 输出上的负载也会影响频率或占空比。

计算振荡频率的简单公式为0.721/(RC * C)。 图3中的完整公式也可通过将(Rb + Ron)替换为(RC + ROL)并将(RA + Rb)替换为(RC + Rc)来使用。 ROL 和 ROH 分别是输出 VOL 和 VOH 驱动器的输出电阻;振荡频率将为1/[tc (H)+tc (L)]。

占空比为25%至60%的三个电阻器、A 稳态电路

‘d一个“电荷引脚”电阻器(RD)将有助于减少输出占空比,因为它会增加放电电阻。 由于 RA 和 RD 的分压器、RD 可降低放电电压幅度。 放电电阻为 Rb +(RA||RD)、放电电压与电源电压之比等于2/3–RD/(RA+RD)。 所需的放电斜坡为电源电压的1/3。 放电时间为 C*(Rb + RA|RD)*-ln (1-1/3/(2/3–RD/(RA+RD))。 这简化为 C*(RB+RA*RD/(RA+RD))*ln(2*RA-RD)/(RA-2*RD),这仍然很复杂。 充电时间与标准设置相同(RA + RB)* C* ln (2)。 该方法适用于所有类型的计时器。

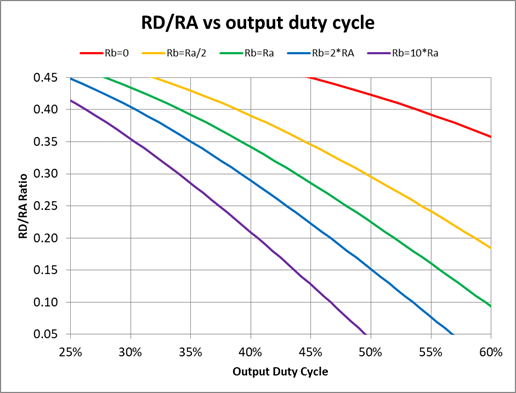

所有三个电阻器(RA、RB 和 RD)都控制该电路的输出频率和占空比、如图5所示。 首先选择(RA+RB)和 C 以获得所需的输出高电平时间。 然后从图6和图7中绘制的五个 RB/RA 比率[0、½、1、2和10]中选择一个。 最后、选择获得所需占空比所需的 RD/RA 比率。

图6. 电阻器比率[0、½、1、2和10]与输出占空比间的关系

图7显示了与图6相同的数据、不同之处在于占空比范围限制在25%至60%之间。 图中省略了低于25%的占空比、因为 RD/RA 比率渐近接近0.5、如图6所示。 此图中省略了大于60%的占空比、因为图1中的两个电阻器(RA 和 RB)电路更适合该输出。 产生50%占空比的标量[RA、RB、RD]有三种常见选择:[9、9、2]、[1、2、 0.15]和[2、1、0.59]。 最后两组电阻器非常适用于标准1%电阻器选择。

图7. 建议占空比范围内的电阻器比率[0、½、1、2和10]与输出占空比间的关系

使用二极管时占空比小于50%

在标准电路中,计时器的高电平时间通过 RA 和 RB (串联)对电容器充电,而低电平时间通过 RB 对电容器放电。 因此、正占空比可以介于50%和100%之间。 额外的转向二极管可以通过旁路 Rb 实现更低的占空比。 然而、由于二极管而产生的电压损耗对温度敏感;因此输出占空比和频率将具有更大的温度系数。 图8显示了包含转向二极管的电路示例。

输出高电平时间由 RA 和二极管压降(VD)设置、而低电平时间由 Rb 设置。 电容器 C 可在低电平和高电平时间内均匀缩放。 就像标准 A 稳态电路一样、低电平时间为 rb * C * ln (2)、高电平时间为(ra + rb)* C* ln (((2VS-3VD)/(VS-3VD)))、其中 VS 为电源电压、VD 为二极管电压。 随着电源电压的增加、VD 项变得不太重要。 随着电源电压降低、VD 项变得更加重要。 对于非常低的电源电压(其中 VS < 3 * VD)、计时器永远不会振荡。

可下载的 TLC555计时器工具

德州仪器提供了一 种特殊的计时器工具 、可帮助客户进行 TLC555计时器设计。 该工具包括传播延迟(Tphl 和 TPLH)和放电晶体管导通电阻(Ron)、可选择与实际器件性能更接近的组件。 内部参数的默认值反映了 TLC 性能。 对于其它计时器,请使用所需计时器的值设置“内部参数”单元格。 该工具还支持添加二极管以实现低占空比输出。

第一个 A 稳态脉冲可能更长

通常被忽略的是、初始脉冲高电平时间将比连续的高电平脉冲更长。 第一个高电平脉冲将延长59%、ln (3)/ln (2)。 通常、计时电容器电压在上电或复位释放后(类似于单稳电路)从0V 开始、而其余所有周期将从1/3电源电压开始。 图10是用于图11中波形的基本 A 稳态计时器电路。

如果控制电容器和计时电容器被成对适当缩放的电容器替换、则第一个高电平输出将与连续脉冲宽度相同(如图12所示)。 与输出高电平时间相比、上电应该很快、但不是瞬时的(如图13所示)。 两个电容器对形成了一个电容分压器、可将计时节点偏置为1/3 VDD、并在加电时将节点控制为2/3 VDD。 总时序电容为 C = C2 + C3。

原始单电容器有助于将计时器比较器与电压引脚上可能存在的噪声隔离。 但是、电容器对会将电源噪声耦合到计时器比较器。 2/3的 VDD 噪声出现在控制引脚和阈值比较器上;而1/3的 VDD 噪声出现在计时电容器节点和触发比较器上。 请注意、耦合噪声会增加输出脉冲抖动。

图13. C2 = C4 = 2nF 且 C1 = C3 = 1nF 时的加电仿真

交换图14中的电容器 C2和 C3将强制输出在低电平启动。 第一个脉冲将具有与图15中的连续脉冲相同的周期和占空比。 与输出低电平时间相比、上电应该很快、但不是瞬时的。 电容器对形成电容分压器、以将计时节点和控制引脚节点偏置到2/3 VDD。 总时序电容为 C = C2 + C3。

两个电容器对将 VDD 噪声耦合到计时器比较器。 控制引脚、阈值比较器和计时电容器节点上存在2/3的 VDD 噪声。 1/3的 VDD 噪声出现在触发比较器上。 耦合噪声会增加输出脉冲抖动。

图15. C3 = C4 = 2nF 且 C1 = C2 = 1nF 时的加电仿真

图16中所示的设置更复杂、消除了 VDD 噪声耦合路径并支持复位引脚切换。 在复位释放后加电时、所有输出脉冲将相同。

R1 || RB 和 R3生成1/3 VDD 基准电压、该基准电压通过 T1、然后在复位电压较低时传递到计时电容器 C。 复位输入可在0V 和 VDD 之间切换以控制输出流。 复位 VIH、电压输入高电平、需要大于2/3 VDD 才能使计时电容器达到阈值输入电平。

‘延迟加电启动,在“复位引脚”上添加一个电容器接地。 为了使 T1有足够的开启余量、VDD 必须至少为3V。 一旦输出变为高电平,D2和 R4将更快地上拉‘reSET Pin’电压。 当使用复位电容器时、建议使用 D2和 R4;这些组件不需要用于时钟复位输入信号。

通常、RA、RB 和 C 设置输出流的频率和占空比。 计时电容器预充电时间是可选的。 ‘预充电时间,“t”,该时间小于最小复位低电平时间。 设置 R1 = t /(C * 2),其中‘C’是计时电容。 对于确保 T1饱和的基极电流、设置 R2 = R1 * 7。 如果 VS > 8V、则使用基极发射极保护二极管 D1。 在 R1、R2和 RB 的负载电流下、R3的精确值对于获得1/3 VDD 基准至关重要。 ‘‘D1未使用时的因子 k’=(VDD–1.8V)/VDD,而 D1二极管实施时的因子‘k’=(VDD–3.6V)/VDD。 然后设置 R3 = 2 /(1/R1 + 1/RB + k/R2)。 ‘用 PMOS 替代 T1,使“k”因子为零。 对于 PMOS 晶体管、R2是可选的、D1二极管不能使用。

最大频率

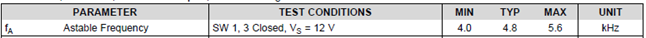

CMOS‘m表具有“最大频率”规格的典型值。

在这两种情况下、测试条件均使用 RA = 470Ω Ω、Rb = 200Ω Ω、C = 200pf。 这些值将在一个无限快的定时器上产生8.3MHz 的频率。 因此、实际频率反映了计时器的最大频率。 只有 TLC 计时器具有最小值。 双极定时器没有最大频率规格。 数据表‘典型特性’部分的图表提供了指导。 100kHz 是图表上的最高频率。

图17. 输出频率与计时电容间的关系、适用于双极和 CMOS 计时器

最低频率

可‘的‘‘d频率基于计时电容器中的泄漏、偏置电流以及计时器的“阈值引脚”、“触发引脚”、“电荷引脚”和 PCB 中的泄漏。 如果 PCB 可能发生冷凝、则电路板可能是最大的泄漏源。 泄漏也会影响频率的精度、因为泄漏会改变有效的电容器充电和放电电电流。

双极定时器中的‘阈值引脚’和‘触发引脚’将开始消耗接近阈值和触发电压的偏置电流,如图18的时序窗口行所示。 因此、在电容器电压斜坡结束之前、偏置电流不会影响充电电流。 充电电阻器电流需要大于阈值引脚电流。 CMOS 计时器没有偏置电流。

图18. ‘双极‘阈值引脚’和触发引脚’输入偏置电流与 Vs 为5V 的引脚电压间的关系

由于需要大电容来实现极低频率、 因此可以 使用纳米计时器作为低频应用的替代方案。 它们只需要一个电阻器即可将延时时间设置为2小时、并且功耗极低。 另一种选择是将计时器输出传递到 表1中列出的逻辑多级纹波计数器、以获得具有小计时器电容值的最终极低频率输出。 CD4060B 具有自己的振荡器。 因此可能不需要555计时器。

|

器件型号 |

最大分压器 |

输出数量 |

包括振荡器 |

|

CD4024B |

128 |

7. |

否 |

|

CD404040B |

4、096 |

12. |

否 |

|

CD4020B |

16 384 |

12. |

否 |

|

CD4060B |

16 384 |

11. |

是的 |

表1. 纹波计数器选项可扩展最小频率或减小计时电容。

精度

在大多数情况下、时序电容器的容差将是时序变化的最大来源。 陶瓷定时电容应为 C0G/NP0类型、以获得最佳温度系数、电压调制和老化特性。 计时电阻器的容差和温度系数也很重要。 应用频率越高、影响输出频率的传播延迟越多。

初始 A 稳态时序精度对于 TLC 通常为1%、SE 为1.5%、LM、NA、NE、SA 为2.25%、对于 LMC 则未指定。 TLC 的最大频率误差为3%、LMC 为17%、这是非常悲观的。 所有精度均基于25°C 值、数据表中的温度系数仅为典型值。 对于整个温度范围内最终精度优于5%的情况、改善计时电容器和电阻器的成本可能高于 晶体振荡器 和 逻辑多级纹波计数器的成本。

LMC555、计算[4.0/4.8-1 =-17%;5.6/4.8-1 =+17%](数据表修订版 M)

控制电压

‘CONTROL’引脚电压在内部生成,通常为 VS 的2/3。控制电压可强制为不同的电压。 频率和占空比都将随控制电压的变化而变化。 在控制引脚上添加电容器有助于在电源电压噪声较大时减少抖动。 加电时、控制电容器将根据控制引脚和控制电容器的阻抗滞后电源电压。 ‘表未指定控制引脚阻抗;有关25˚C 和 VS = 5V 时控制引脚’阻抗、温度系数和电压系数的示例数据,请参阅表2

|

计时器 |

阻抗 |

温度系数 |

电源系数 |

|

单位 |

kΩ μ A |

%/˚C |

%/V |

|

LMC |

60 |

0.75 |

0.39. |

|

TLC |

52. |

0.48. |

-2.60 |

|

Lm |

3.3. |

0.15 |

0.06. |

|

NA、NE、SA |

3.3. |

0.18. |

0.08 |

|

SE |

1.6. |

0.16. |

0.05 |

表2. 在25˚C 且 VS = 5V 时采样数据‘控制引脚’阻抗

复位输入

当‘reSET Pin’(设定引脚)电压变为低电平时,输出也会变为低电平。 “‘d引脚”也将变低,计时电容器将通过电阻器 RB 放电。 ‘re将保持低电平,直到“SET Pin”恢复为高电平。 当复位变为高电平时、如果计时电容器电压低于1/3 VS、输出将变为高电平。否则、输出将保持低电平、直到计时电容器电压降至1/3 VS。