主题中讨论的其他器件:LMK04906

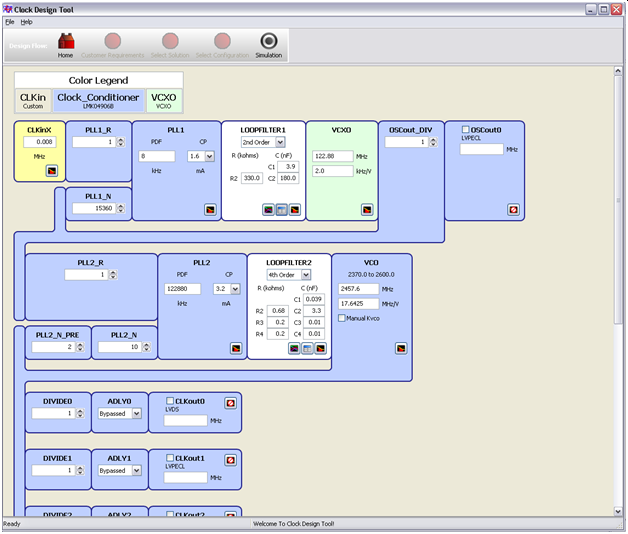

我正在评估 LMK04906 (使用 TI 评估板) 、以便生成与 TI TSB82AA2BI 1394b 链路层控制器生成的8kHz 时序参考同步的32.768MHz 和16.384MHz 时钟。

LMK04906 单路 PLL/内部 VCO 设置可用、 并且 LMK04906 成功 地将输出时钟锁定到8kHz 基准、 并在 LLC 在1394总线上"主器件"时将 Status_LD/PLL2 DLD 置为有效(8kHz 基准上的抖动极小)。

但是、 如果这个特定的 PHY 是1394总线上的"从器 件"(在8kHz 基准中产生高达500ns 的周期来循环抖动)、输出时钟仍然实现到输入的锁定、但是 Status_LD/PLL2 DLD 输出不稳定、在锁定和解锁之间发生变化。

是否有任何器件设置可通过抖动基准输入来稳定 DLD 运行?

Danny