大家好、

我的客户正在使用我们的 LMK03328、并想向您咨询如下用户案例。

当前在正常切换到模式1 (设置附件等文件)时遇到的问题、

e2e.ti.com/.../mode1.txt

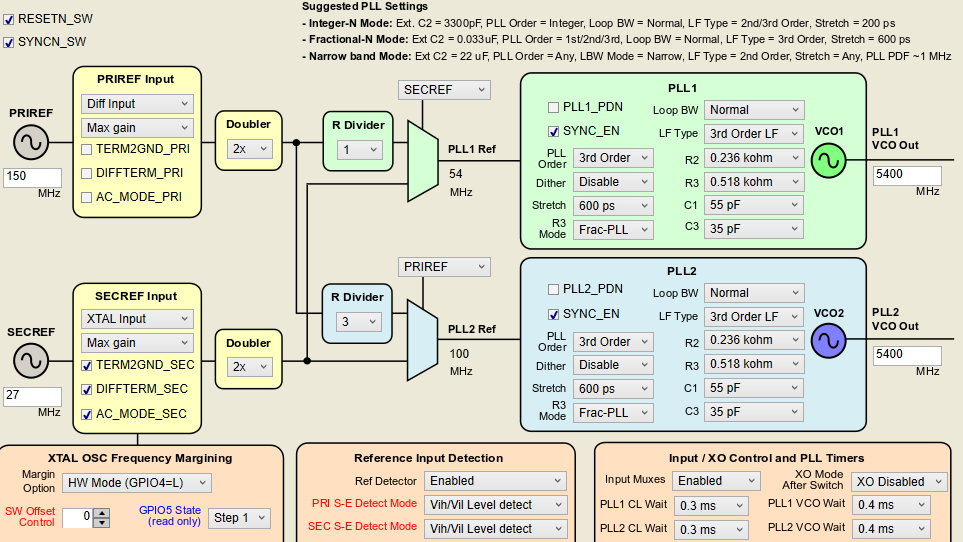

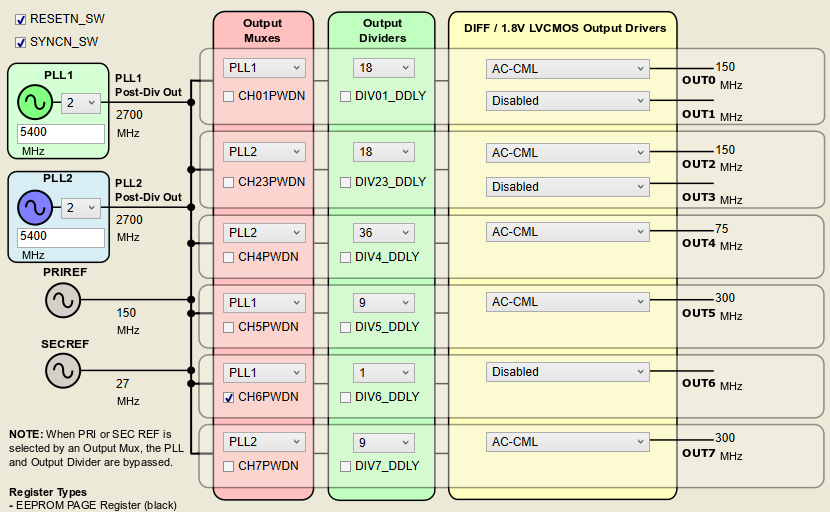

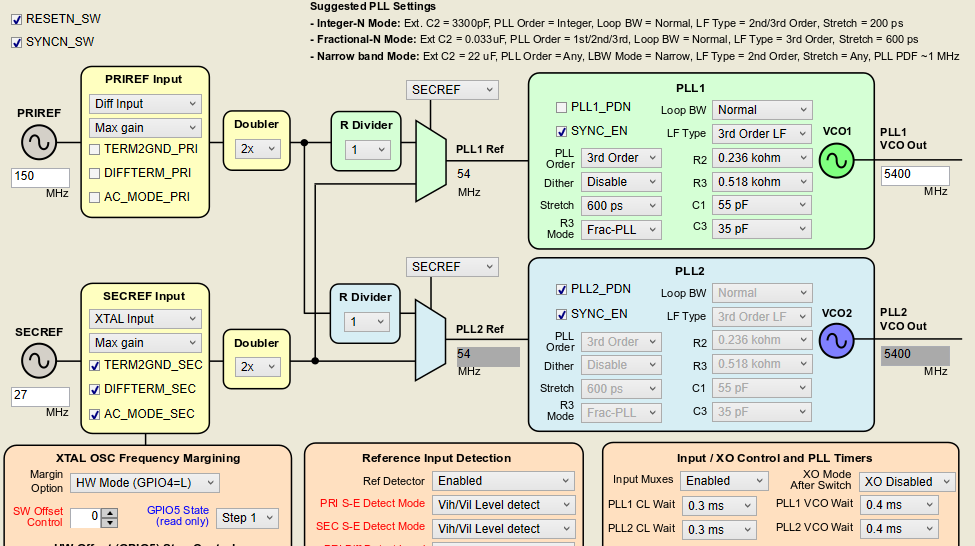

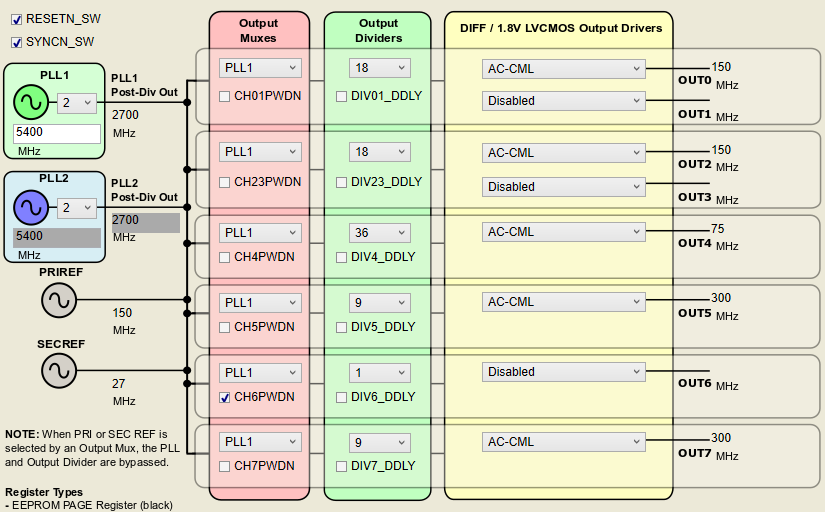

更改的唯一设置是调整与 PLL2相关的设置、

但是、您仍然会看到显示解锁现象的 PLL1状态(紫色通道、如下所示)、

并使原始输出时钟中断一段时间(下图中的黄色通道)、

设置过程:PLL2断电使能-> PLL2和分频器设置-> PLL2断电禁用

我们想咨询您 、LMK03328内的 PLL1和 PLL2是否都是不会相互影响的独立通道? 如果是、在切换 PLL1和 PLL2时、应遵循哪些设置程序来避免相互影响?

还想咨询您、是否有任何建议的相位裕度范围来确保 PLL 的稳定性? 感谢你的善意帮助。