您好!

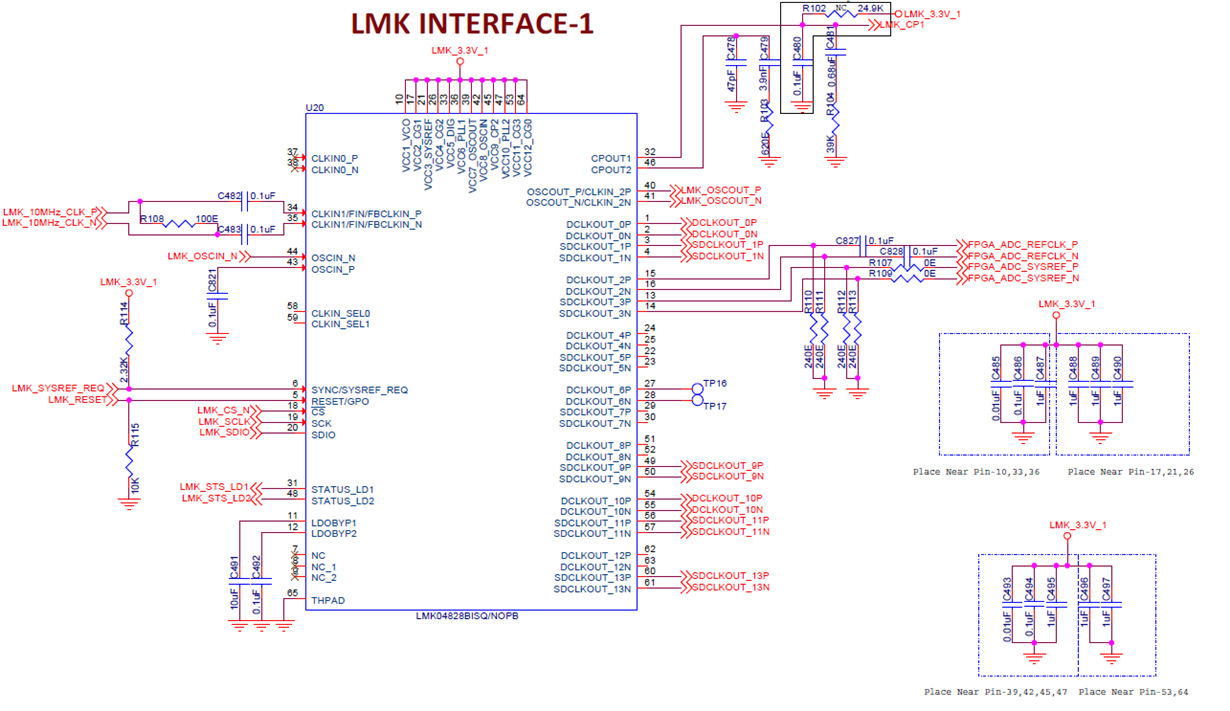

我在定制电路板的设计中使用了 lmk04828b、为 OSC 引脚提供了100MHz 时钟。 我已经有 lmk EVM 套件。 当通过给定套件部分的电缆通过汽车专业版启动时、我们定制板中的 Lmk 不起作用。 我已经检查了板载复位、它通过10k 拉低。

我们提供的 OSC 时钟从 OSC 流出 lmk、因此 lmk 的时钟输入似乎正常。

我们尝试通过三线制 SPI 对器件进行编程、dclk/sdlk 不会产生时钟。

此时、我不知道要检查什么。

我们没有使用 clk SEL 引脚、它保持开路。

在 CP 输出端、我们测量的是1.8V

当我们进行探测时、对芯片和来自专业技术人员的控制进行偏置似乎是可以的。

请帮助。

此致、

Rajesh Khanna。