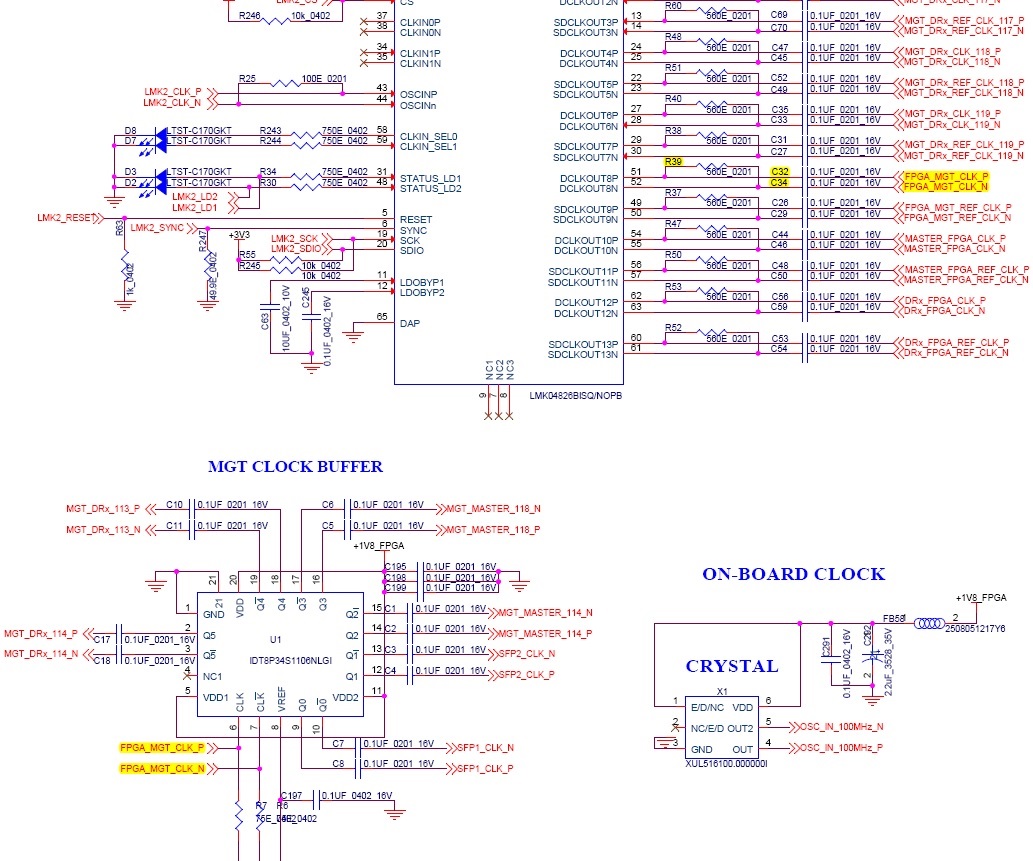

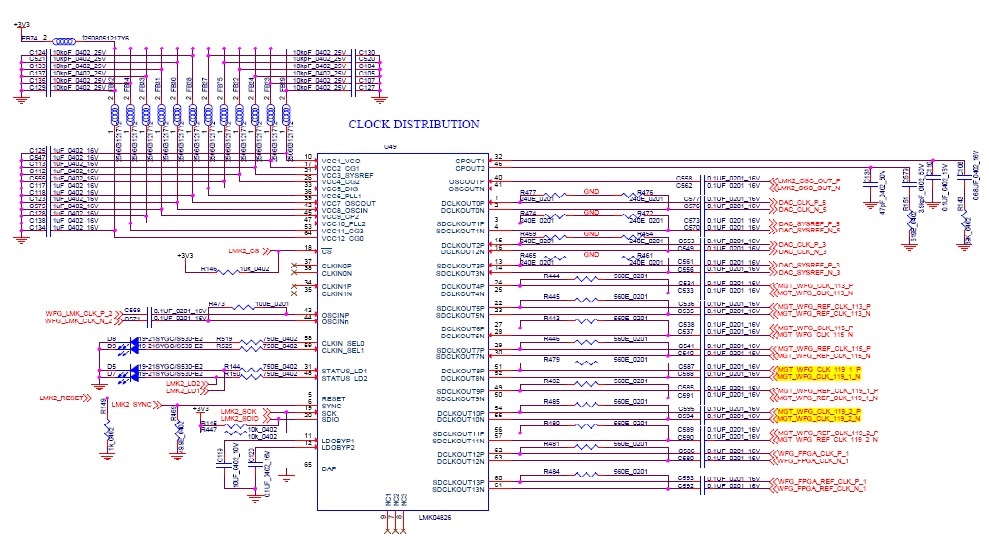

我已经对 lmk 进行了编程,以提供156.25MHz 的 LVDS 输出,这是我在 Virtex 7 FPGA 中的管理库所提供的。

然后、我将该时钟用于 Aurora IP 内核和以太网子系统 IP 内核、但两个 IP 内核都显示没有 PLL 锁定。 为了进行测试、我将156.25MHz 的晶体振荡器作为 FPGA 的输入时钟、在此期间两个 IP 内核都显示 PLL 锁定。 我需要使两个 IP 内核都可以使用 lmk、但无法使其正常工作。 我已附加了两个时钟的屏幕截图

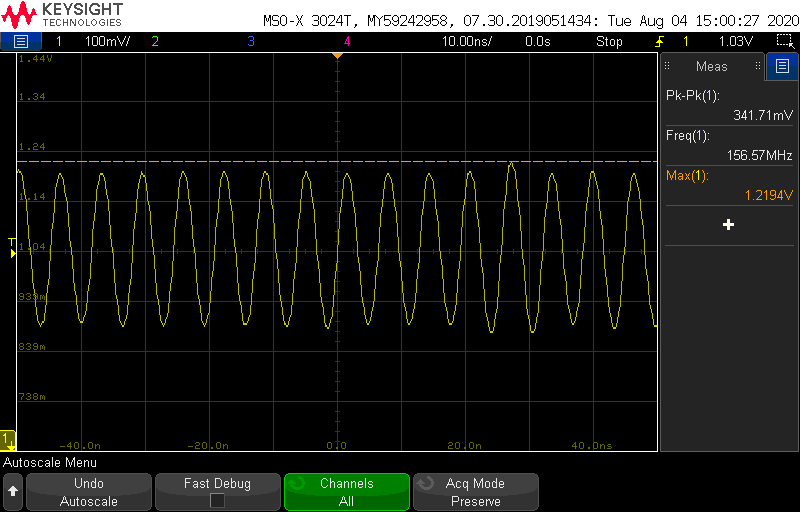

OSC 时钟 P

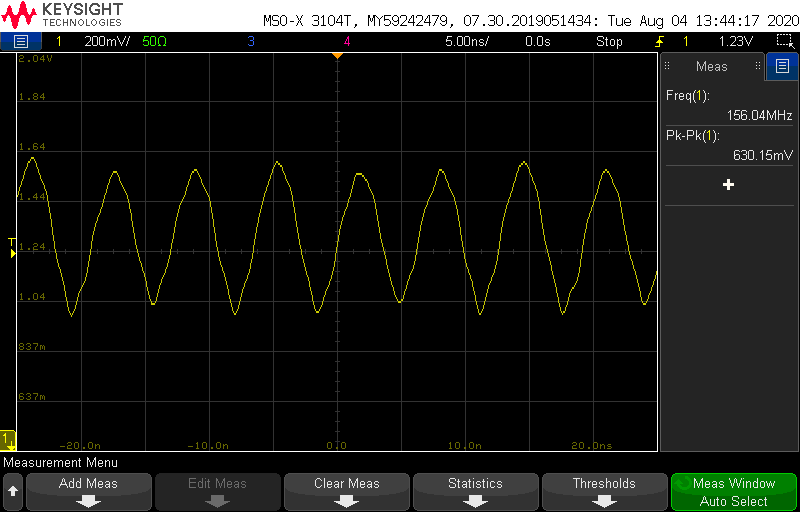

下图显示了我从 lmk 的 LVDS 线路之一获取的 clk 输出。

下图显示了我从 lmk 的 LVDS 线路之一获取的 clk 输出。

LMK 时钟 P

请给出建议。