主题中讨论的其他器件: LMX2820、 PLLATINUMSIM-SW

您好、TI 专家、

我有3个关于 lmx2594的整数边界杂散(IBS)问题、

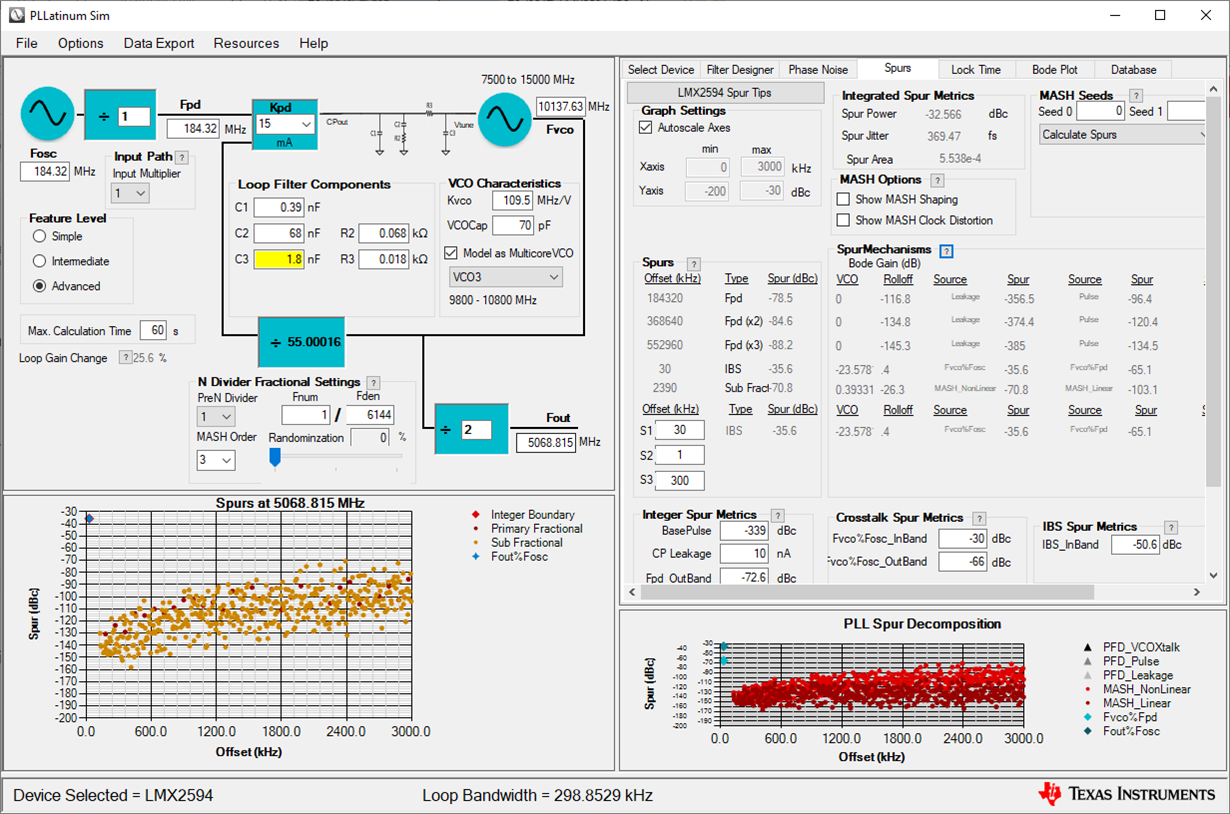

当我将 FPD=184.32M 和 FDEN=184320时、在 PLL 输出为10137.63M 时、有一个30kHz 偏移的大 IBS。 我可以在这里了解30K IBS。

为了避免10137.63M 时出现 IBS、我将 FPD 更改为221.184M、但在10137.63M 时仍有30kHz 杂散。 我不知道为什么杂散仍然存在。

根据我的理解、Fvco/FDP=10137.63/221.84=45.833469、它不靠近 整 数通道、因此不应存在整数边界杂散。

2.有否其他方法可避免使用智能大厦系统?

如何区分 PLL 主导或 VCO 主导的 IBS?

谢谢。