您好!

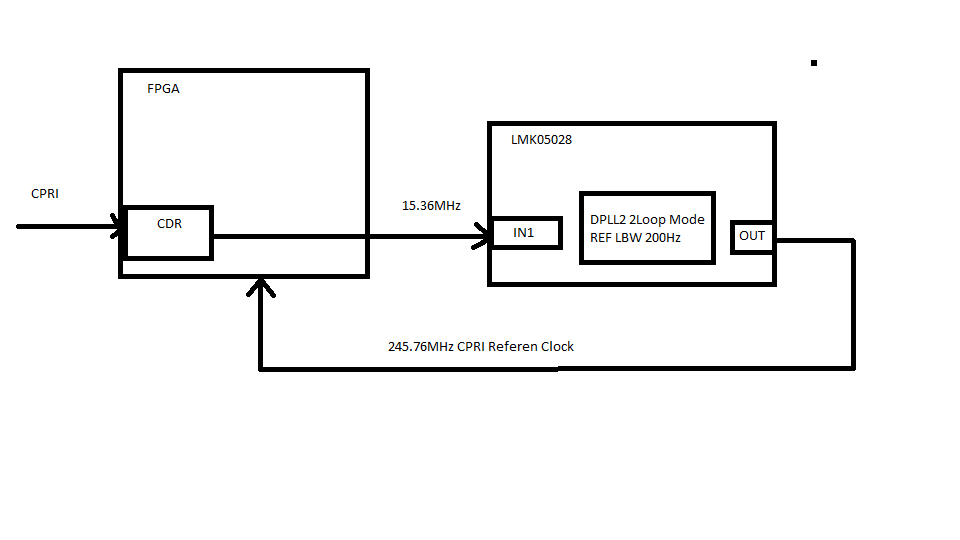

我在 CPRI 应用中使用 LMK05028作为抖动清除器、如下图和.TCS 文件所示。

正常运行:通电时插入 CPRI 电缆。 CDR 频率为15.36MHz、即 LMK05028锁的 DPLL2

然后拔下 CPRI 电缆、CDR 频率降至15MHz (无数据可恢复)

然后插入 CPRI 电缆、CDR 频率恢复为15.36MHz、但 DPLL2冻结、不锁定。 我读取 PLL2_STATUS_NUM、全部未更改。 当输入基准超出 DPLL 的拉入范围时( PLL2冻结时、根据 PLL2_STATUS_NUM 进行的计算值约为2000ppm)、PLL 冻结并且无法恢复。

您会建议什么来解决该问题? PLL 可以自动恢复。