主题中讨论的其他器件: LMX2594、 TIDA-01023、 LMK04832

大家好、

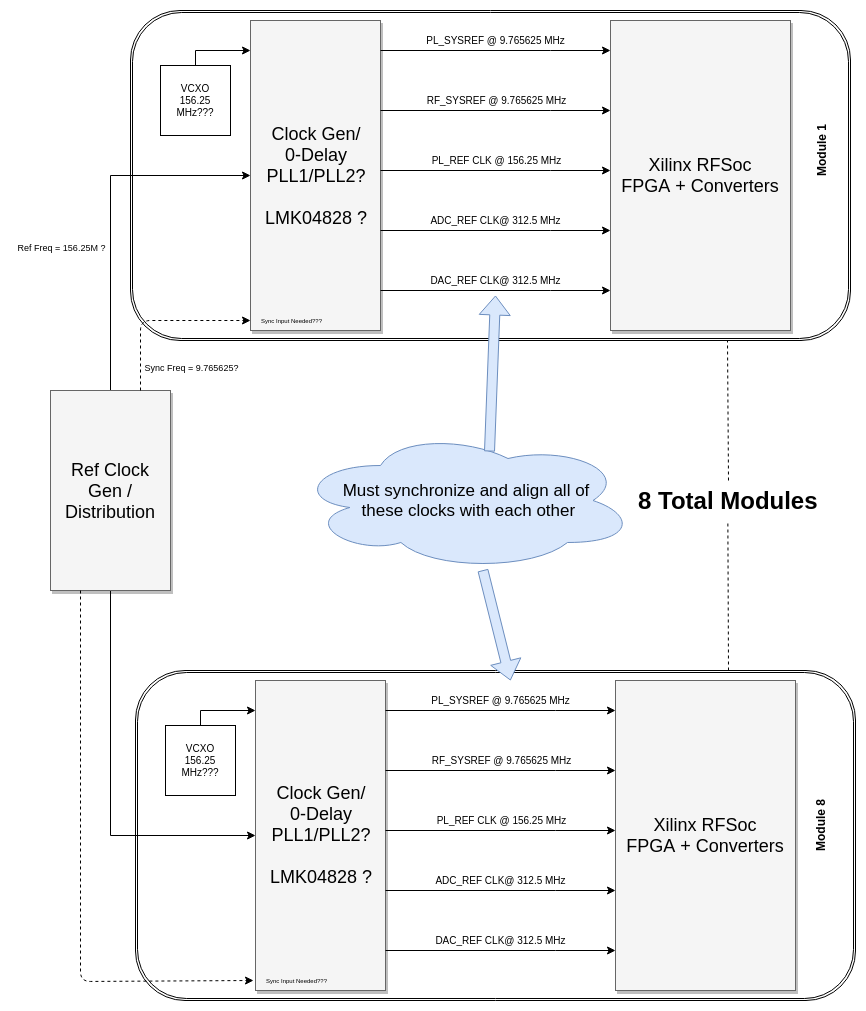

我们正在设计一个将有8个 Xilinx RF3200同步的系统。 Xilinx 代表告诉我、RFDF充当 JESD204B 转换器的转换器同步结构。 8个模块(每个模块都有 RF必 将被安装在一个负责分配公共信号和时钟的中央计算板上。

初步设计需要156.25MHz 系列的时钟、模块射频时钟频率为:

- ADC 和 DAC REF Clk = 312.5MHz

- PL REF Clk = 156.25MHz

- PL_SYSREF & RF_SYSREF = 9.765625MHz (每个 Xilinx 的该频率必须小于10MHz)。

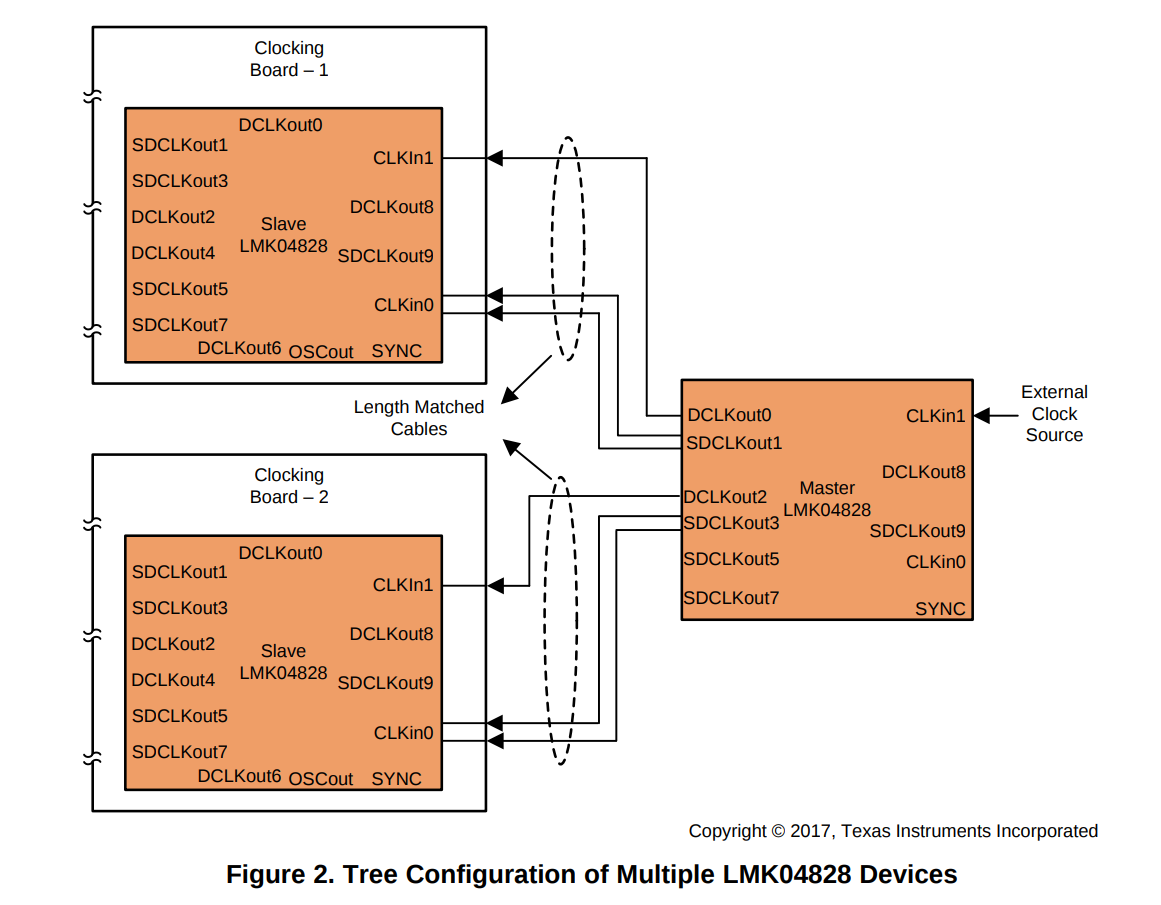

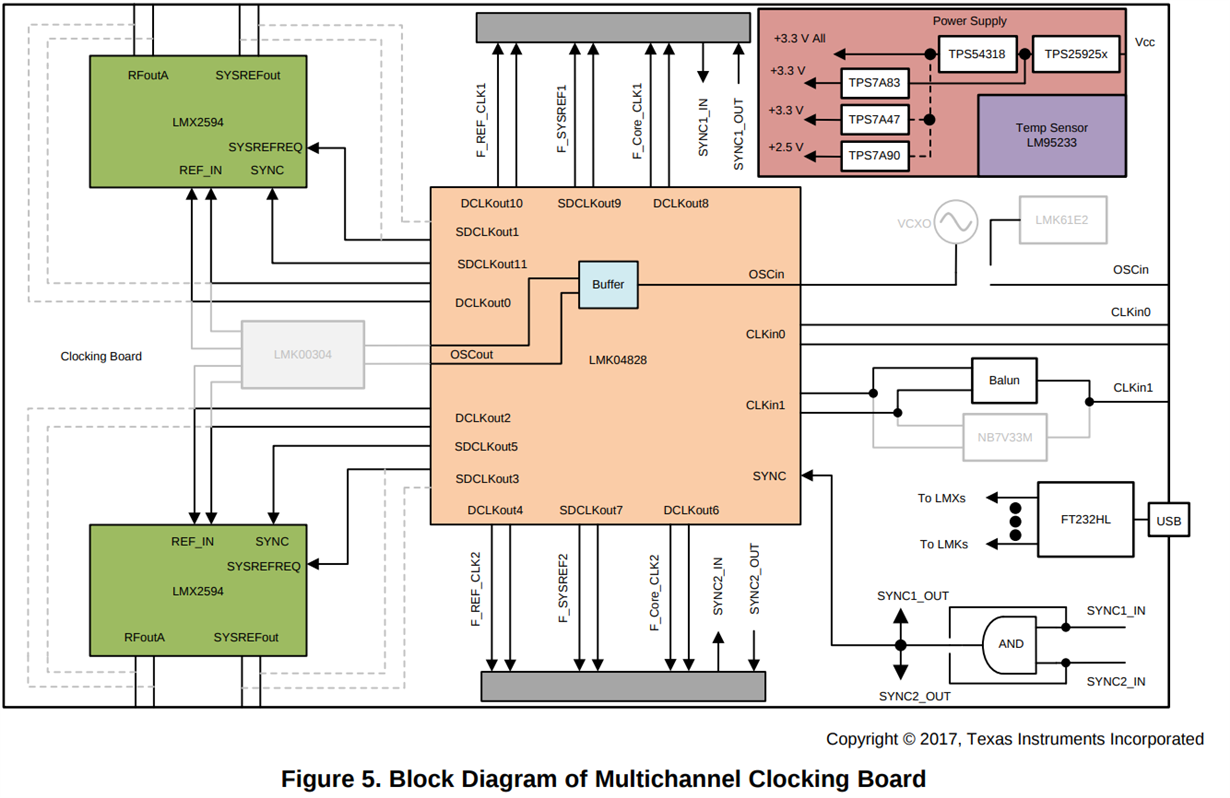

要求不仅在模块中、而且在所有模块中使所有这些单独的时钟同步并对齐相位。 目标抖动< 50ps、且可能的相位偏移量最小。 我已经在 这个论坛上阅读过很多关于零延迟模式下 LMK04828的文章、我认为这可能是最好的解决方案、但是我不确定这些频率是否可行、以及最好使用什么零延迟模式。 我一直在使用 TICS Pro 软件、但它不允许我达到这些频率、我不确定要使用的最佳 VCXO 频率。 这些想法和价值观都是极好的。

下面是当前想法的概述图:

如果所有 LMK04828模块都处于零延迟模式、并且由相同的参考时钟馈送、是否需要输入 SYNC 信号?

感谢您提前观看、

-Jim