你(们)好

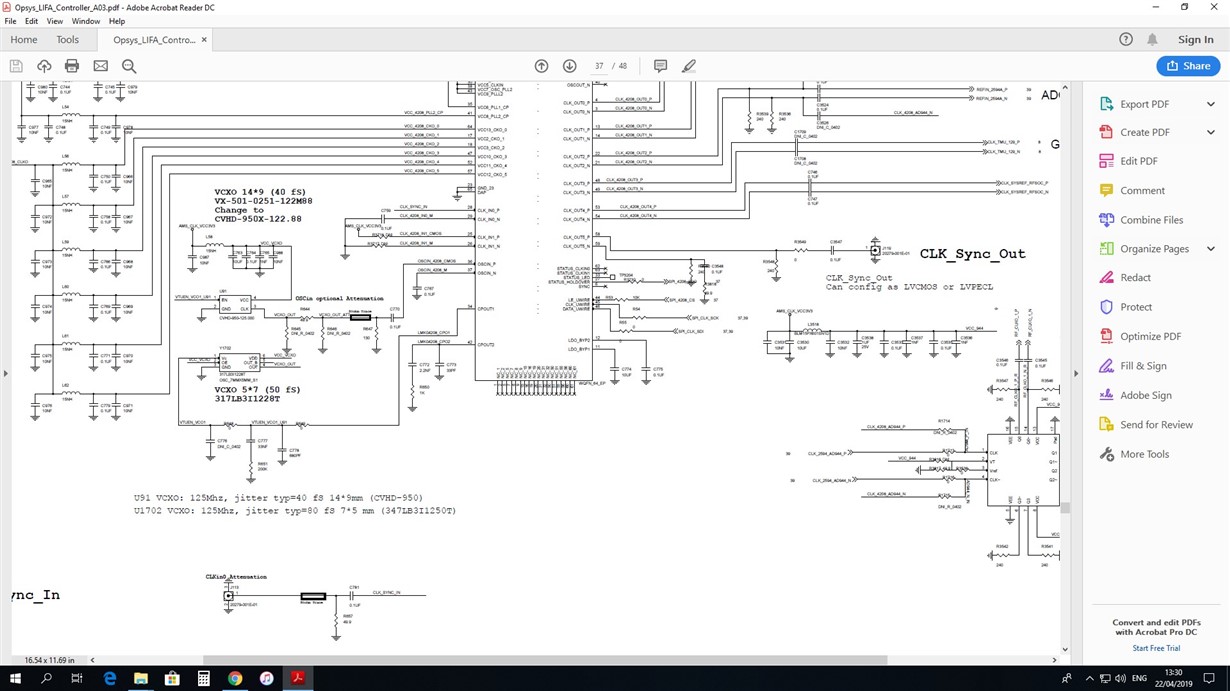

在我们的设计中,我们使用 LMK04208来驱动 Xillinx FPGA,其设计与 使用外部 VCXO 的 LMK04208评估类似。 我们使用两个类似的卡、第一个卡是主卡、在以下配置文件中作为待机模式运行、第二个卡是从卡、其中主卡125MHz 同步时钟驱动从卡 clk_in_0输入。

我们有4个运行卡、每个卡都可以充当从卡(在这里它锁定到主125MHz 时钟)、但4个卡中的一个无法(作为主卡)推送其他3个卡!!!

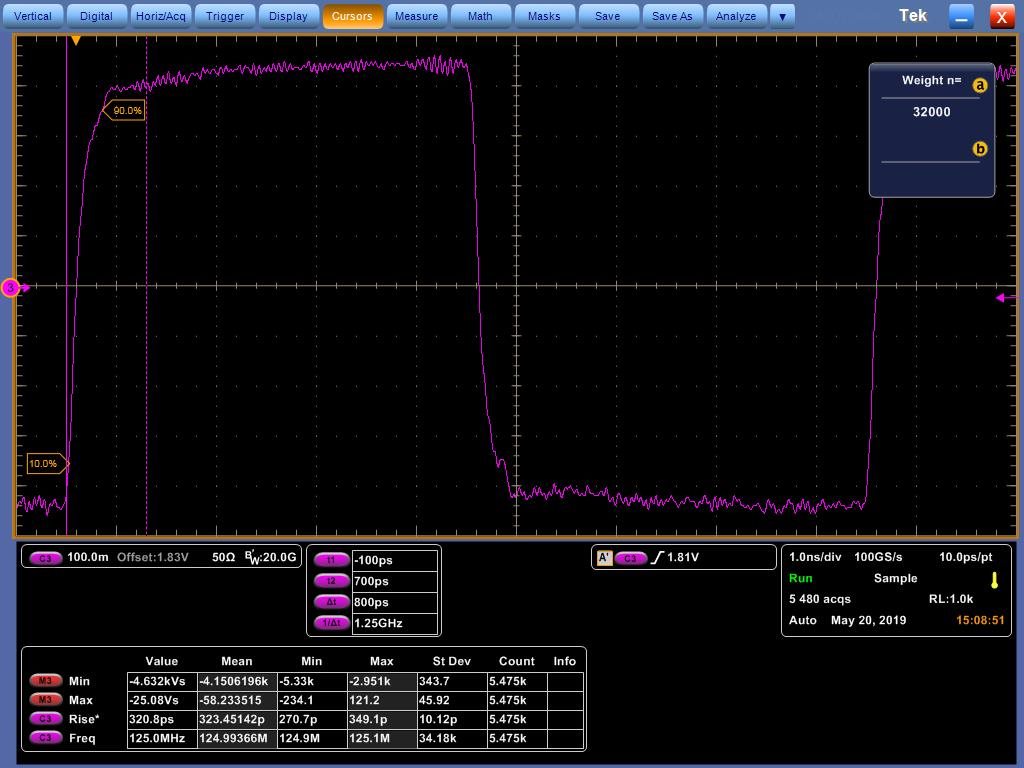

当使用20GHz Scoop 处理 LMK04208输出时、我们几乎看不到任何差异

您是否知道导致此问题的原因?

我们如何检查 LMK04208的抖动输出?

主配置(其中,对于从配置,我们仅将输入从 clk_in_1输入更改为 clk_in_0输入) :

R0 (INIT) 0x00160040

R0 0x00140300

R1 0x00140301

R2 0x00140062

R3 0x80140603

R4 0x00140304

R5 0x80140185

R6 0x01100006

R7 0x01300007

R8 0x04010008

R9 0x55555549

R10 0x9102410A

R11 0x0401100B

R12 0x1B0C006C

R13 0x2302826D

R14 0x0200000E

R15 0x8000800F

R16 0xC1550410

R24 0x00000058

R25 0x02C9C419

R26 0xAFA8001A

R27 0x10001E1B

R28 0x00201E1C

R29 0x0180019D

R30 0x0200019E

R31 0x003F001F

谢谢

Oded