Other Parts Discussed in Thread: CDCLVC1106, SN65LVDT14

主题中讨论的其他器件: SN65LVDT14

大家好、团队、

您能帮助回答以下问题:

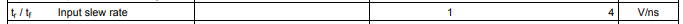

需要对 CDCLVC1106时钟缓冲器的数据表压摆率规格进行澄清。 我们计划将此部件用于 TI SN65LVDT14 LVDS 收发器的下游,用于传输到6个 SPI 从器件的 SPI 时钟信号。 但是,时钟缓冲器具有有关最大输入压摆率的规格,这种规格似乎会使其与3.3V 电源下 LVDS 收发器的最小输出上升/下降时间不兼容。

LVDS 收发器:

时钟缓冲器:

我们以前没有看到过这样的缓冲器上的最大输入压摆率规格,因此我们想知道如果超出最大值,风险和潜在故障模式可能是什么。 您能告诉我们、如果将这些部件一起使用会有问题吗?