大家好、

我们客户的问题之一、我在下面转发、 您能否提供一些故障排除建议

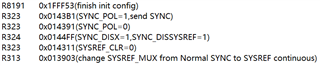

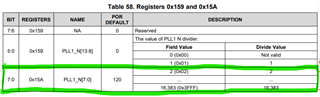

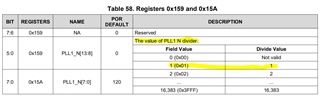

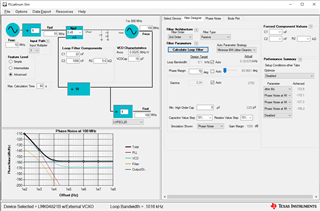

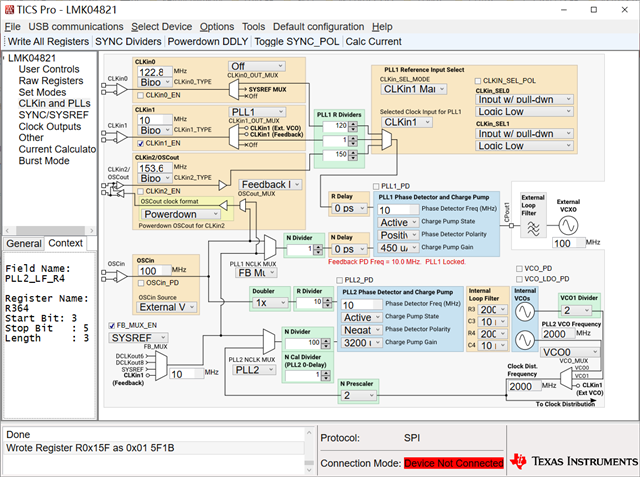

使用 lmk04821、在双 PLL 级联零延迟模式下工作、TICS pro 配置文件为 lmk04821_config.TCS..参考时钟输入是一个10MHz、5dBm 正弦波、从 CLKin1输入。 通过 FPGA 从芯片 IO 输出获取 PLL_DLD 信号。 发现 PLL1偶尔失锁、之后大约为0.16ms、然后再次锁定;PLL2始终处于锁定状态。 我是否可以知道 PLL 1失锁的可能原因、以及它是否未以正确的方式进行配置。

此致、

罗美