主题中讨论的其他器件:LMX2595

您好!

在这里、我使用的是类别3中的 LMX2595、参考 OSC 频率在限制范围内。 我从外部脉冲发生器提供了 SYNC s/g (1MHz),但看不到确定性相位。 是否有人可以澄清我的以下问题

1.在数据表中,有人提到它是时间关键型的。 我如何才能做到这一点? (希望在实验室中查看)

2.在相位同步参考设计中,设置时序关键示例的步骤是什么?

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

在这里、我使用的是类别3中的 LMX2595、参考 OSC 频率在限制范围内。 我从外部脉冲发生器提供了 SYNC s/g (1MHz),但看不到确定性相位。 是否有人可以澄清我的以下问题

1.在数据表中,有人提到它是时间关键型的。 我如何才能做到这一点? (希望在实验室中查看)

2.在相位同步参考设计中,设置时序关键示例的步骤是什么?

谢谢

您好!

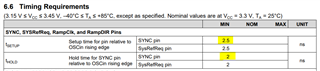

当 LMX在 Cat-3中运行时、为了在 LMX之间 实现确定性相位、需要外部同步输入、并且时间至关重要。 这意味着、SYNC 输入应满足确定性相位的设置和保持时间。 同步上升沿应在 OSCin 上升沿之前的最小值为2.5ns、并应保持高电平直到2ns、以满足同步时序要求。

关于上述参考设计、第4.2.1节给出了非时序关键同步输入(Cat-2同步)示例、该示例不需要满足设置和保持时间要求。 而第4.3节显示了时序关键型同步的示例、其中 SYNC 输入应以 OSCin 输入为基准、并满足设置和保持时间要求。

谢谢!

此致、

Ajeet Pal

您好、Rajani、

您的同步信号是否满足设置/保持时间要求?

请查看以下 EVM 用户指南以了解 Cat3同步示例。