主题中讨论的其他器件: LMK00334

LMK00338 8路输出 PCIe 时钟缓冲器有问题。 产出因未知原因"死亡"。

例如、某些输出的正桥臂或负桥臂的摆幅可能会达到满摆幅的一半左右。 一些输出没有响应(死区)。

此外、在一段时间(10分钟)后、所有输出可能会失去知觉(有时会发生)。 在短暂断电后、它们将被恢复。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Alex:

感谢您发表您的疑虑。 这不是器件的预期运行。 您能否分享下面列出的一些其他信息?

当我们获得有关您的操作条件的更多信息以重现问题时、我还会在我的一侧看到类似的行为。

最棒的

阿西姆

您好、Asim、

我在我的系统中使用 LMK00338。 LMK00338的负载是我们的 ASIC。

我同意 LMK00338的这种行为是不可预料的、我确实想知道我做了什么(如果我做了)。

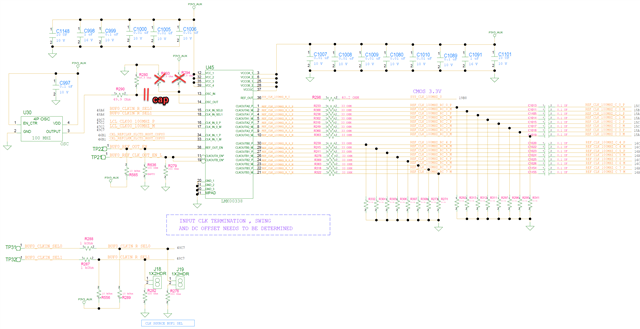

下面是 LMK00338的原理图页面。 我在板上有几个。 该委员会进行了多次返工、但我没有很强的感觉、但这种行为是这些返工的结果。

时钟缓冲器具有全部三个时钟源、可通过跳线(两个2引脚 SMT 接头)进行选择。

时钟输出:我们的芯片需要(推荐)用于 HCSL 逻辑的交流耦合。 这些电容器显示在原理图上并放置在电源附近。 现在、它们通过导线被绕过。

我的顾虑:

我认为没有任何其他对您感兴趣的东西。

有关测量的内容。 我使用具有差分和 SE 探头的示波器。 使用 SE 探头、我可以看到输出时钟信号是如何恶化的。 DIFF 探针用于查看目标上的时钟(当我们的芯片从插座上移除时)。

如果您需要任何其他信息、请告诉我。

谢谢、

Alex

尊敬的 Alex:

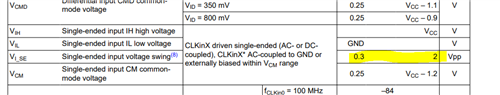

[引用 userid="544435" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1172512/lmk00338-outputs-of-the-lmk00338-pcie-clock-buffer-are-dying-with-time/4412269 #4412269"]输入 SE 时钟摆幅为~3V (在分频器后的 OSC_IN 输入上),但 LMK00338不显示任何摆幅要求。正确的是、OSCin 没有在数据表中指定输入摆幅。 OSCin 与 CLKINX 引脚共享相同的输入结构。 对于 OSCin、也请对 CLKinX 使用单端输入摆幅要求。 OSCin 上的电压应小于2V。 这可能是导致问题的原因之一。

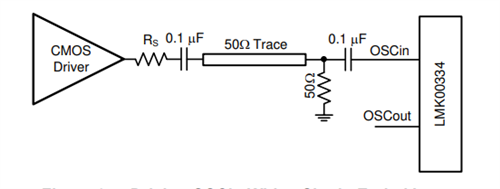

您是否也可以遵循数据中提供的确切终端方案。 CMOS 驱动器之后的第一个电容可防止其看到低直流路径、第二个电容有助于避免 LMK00334的内部直流偏置短路。 根据 CMOS 驱动器类型、可能不需要第一个电容器、但最好使用它来避免这种问题。

您还提到、分压器之后的输入摆幅为3V。 这是分压器之前的3.3V LVCMOS 输出吗? 如果是这样、则表示其输出阻抗非常低。 R290是否作为 Rs 放置以满足驱动器的该要求?

我假设 R636也未被组装、因为我们希望启用 REF_OUT。

我想、总的来说、如果您能够将输入摆幅调节到2V 以下的话。 这将有助于解决输出问题。

请告诉我这是否有助于解决 问题、否则我们可以深入了解。

最棒的

阿西姆

您好、Asim、

实际上、有关 OSC_IN 信号摆幅、我是错的。 我使用了一个好探头、测得的电压约为1.8V。 所以、这不是一个谜。

第一个电容器(在串联电阻器之后)、以消除 OSC 的直流路径。 现在无法添加、因为没有空间、尤其是在 OSC_IN 处添加第二个电容器后。 此外、它看起来 OSC 可以完美地处理100欧姆到 GND。 因此、第一个电容器可能很好、但不需要。

R636未被组装、因为我们使用 REF_OUT。 不再需要。 我们现在还有另一个选择。 仅移除了 R298 (REF_OUT 处的串联电阻器)。 因此、REF_OUT 没有负载。

就规范内 OSC_IN 上的时钟而言、仍然不清楚哪些因素会导致输出失败。

顺便说一下、其余两个输入时钟是合适的 HCSL。 我不明白一个发生故障的时钟源(我看到不是我的情况)如何会导致输出失败、即使选择了另一个时钟源也是如此。

谢谢、

Alex

尊敬的 Alex:

感谢您的反馈。 只需确认一下 、就像您说的那样。

[引用 userid="544435" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1172512/lmk00338-outputs-of-the-lmk00338-pcie-clock-buffer-are-dying-with-time/4412432 #4412432"]R636未被填充、因为我们使用 REF_OUT。 不再需要。 我们现在还有另一个选择。 仅移除了 R298 (REF_OUT 处的串联电阻器)。 因此、REF_OUT 没有负载。[/QUERP]R636未被组装、这是因为您之前未正确使用 REF OUT。 因为电流原理图显示 REF_OUT 已启用。 正常情况下、在时钟输出上启用和禁用时不会出现问题。

[引用 userid="544435" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1172512/lmk00338-outputs-of-the-lmk00338-pcie-clock-buffer-are-dying-with-time/4412432 #4412432">顺便说一下、其余两个输入时钟都是合适的 HCSL。 我不明白一个失败的时钟源(我看到不是我的情况)如何会导致输出失败、即使选择了另一个时钟源。每当通过 输入 MUX 选择可能违反输入摆幅条件的时钟时。 这可能会导致 MUX 出现问题。 但在您的案例中、情况似乎并非如此。

目前您已选择 CMOS 时钟扇出、但在选择其他输入时、您也会看到同样的问题。 这是我需要进一步了解的内容。 我认为您不需要使用接头、也有一个内部下拉电阻器、如果未连接到 VCC、则会使其变为低电平。

您能否确认正常运行以及输出何时开始关闭时的功耗? 我也将复制您在 TI EVM 上的设置。

最棒的

阿西姆

您好、Asim、

我已检查 VDD。 无压降。 我有两个新板、时钟缓冲器很好。

我认为问题可能是由于一些董事滥用职权造成的。 该区域有多个返工。 此外、更换了芯片、装配室使用的是半导体液体、可能未正确清洁。 我在控制引脚18和19之间几乎短路(~2欧姆)、这在触摸后消失。 不确定这会如何影响输出的奇怪行为。 奇怪的是、通道3随着时间完全恢复(它以前在一个桥臂上具有小信号)。

我不确定是否有必要进行更多调查、除非您真的想知道导致此类行为的原因。

谢谢、

Alex

Alex、您好、感谢您的反馈。 我将关闭此主题。 我可能会误解下面的说法。 总之、好的是、它不是器件。

[引用 userid="544435" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1172512/lmk00338-outputs-of-the-lmk00338-pcie-clock-buffer-are-dying-with-time/4416282 #4416282"]我的控制引脚18和19之间几乎短路(~2欧姆)、这是在触摸后发生的[/引用]最棒的

阿西姆