主题中讨论的其他器件: LMK00304

您好,

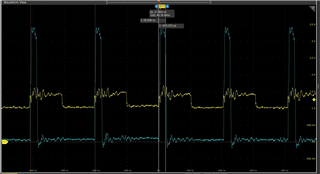

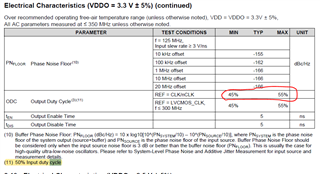

LMK00804B 的输入时钟为具有交流耦合的4.8828125MHz LVDS 时钟、其占空比为~50%(下图中的黄色曲线)。 但输出时钟的 dute 周期不在数据表中提到的45%~55%(蓝色曲线)范围内、如下图所示。 为什么?

提前感谢!!!

此致!

Jason

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Asim:

您的建议可以解决我的问题。

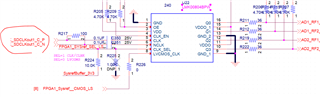

我将0.1uF 容量替换为0欧姆电阻器。 现在 、LVCOMS 输出的 dute 周期 接近50%。 非常感谢!

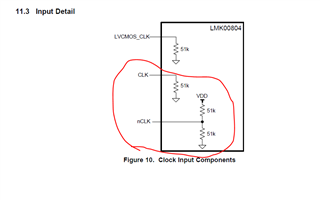

我之所以使用交流耦合输入时钟、是因为我认为 CLK 和 nCLK 在芯片中具有偏置、如下图所示。 所以、这是一个坏主意。

BTW、LMK00804B 的最大输出偏斜为35ps。 您是否有其他建议 使用的时钟缓冲器、这些时钟缓冲器的偏斜小于35ps、 并且1个差动时钟输入至少具有4个 LVCOMS 输出?

您好 Jason、

它取决于您需要的输出格式类型。 我 已筛选出偏移低于35ps 的一些差分缓冲器器件的列表。 您可以使用"查看此列表"根据您的驱动程序类型需求进行选择。 此列表包含新系列的缓冲器以及20ps 或更低偏移。

最棒的

阿西姆