请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK04828BEVM 主题中讨论的其他器件:AFE7906、 LMK04828

我有 AFE7906 ADC,需要通过 LMK04828为 ADC 和 FPGA 提供器件时钟和 Sysref,我们能否同时连接 OSCin 和 CLKIN 引脚

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我有 AFE7906 ADC,需要通过 LMK04828为 ADC 和 FPGA 提供器件时钟和 Sysref,我们能否同时连接 OSCin 和 CLKIN 引脚

您好 Rajashekar、

您可以同时使用 OSCin 和 CLKIN 引脚、但不能同时使用、CLKIN 引脚信号将用作基准或 OSCIN 基准将用作基准。 如果这不是您的问题、请进一步详细说明、以便我可以更好地支持您。

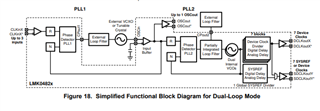

请注意、OSCin 是第二个 PLL 的输入;因此、输入到 OSCin 的基准信号将完全跳过第一个 PLL 并省略其执行的任何抖动消除。 供参考、第一个 PLL 用于清理输入到器件的基准、第二个 PLL 用于生成更高的输出频率。

另请注意、如果您向 OSCin 引脚输入信号并将该引脚用作时钟输入、则通过第一个 PLL 的 CLKIN 输入信号将不会通过第二个 PLL。 请查看数据表第50页的下图、以更好地了解信号如何通过我们的器件传输。

谢谢、

Andrea