你(们)好。

有关 CDC3RL02BYFPR 的两个问题

测试条件。 VBATT 打开、MCLK_IN 为27MHz

当 CLK_REQ 为低电平时、vldo 输出为0.8。 如果 MCLK_IN 被移除、Vldo 变为0v。

在 CLK_REQ 打开后、VLDO 输出时钟有200us 的延迟。

这两种行为是否正常运行?

BRS

Shubiao

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好。

有关 CDC3RL02BYFPR 的两个问题

测试条件。 VBATT 打开、MCLK_IN 为27MHz

当 CLK_REQ 为低电平时、vldo 输出为0.8。 如果 MCLK_IN 被移除、Vldo 变为0v。

在 CLK_REQ 打开后、VLDO 输出时钟有200us 的延迟。

这两种行为是否正常运行?

BRS

Shubiao

您好、Shubiao、

我很乐意为您解答问题。 以下是我对您的问题的意见:

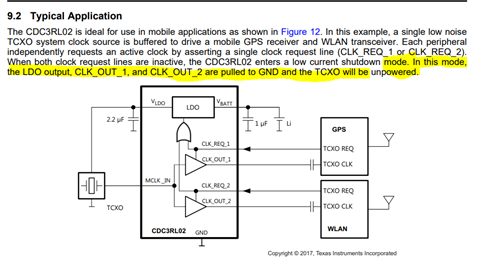

我确实看到数据表在第9.2节中提到当 CLK_REQ_X 为低电平时 VLDO 输出接地。 目前、我不确定 MCLK_IN 移除与 LDO 输出之间的关系。 我需要通过查看内部电路从芯片设计人员那里了解这一点。 在方框图中、 由于 LDO 断电、因此当没有 CLK_REQ_X 时、它应该变为低电平。

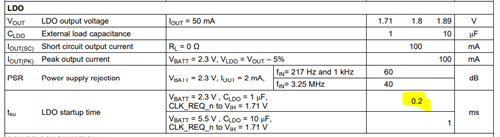

当 CLK_REQ_X 被启动时、VBATT = 2.3V 时、LDO 启动时间大约为200us。 这种行为应该是正常的。 请确认您是否使用相同的 VBATT 条件。

最棒的

阿西姆