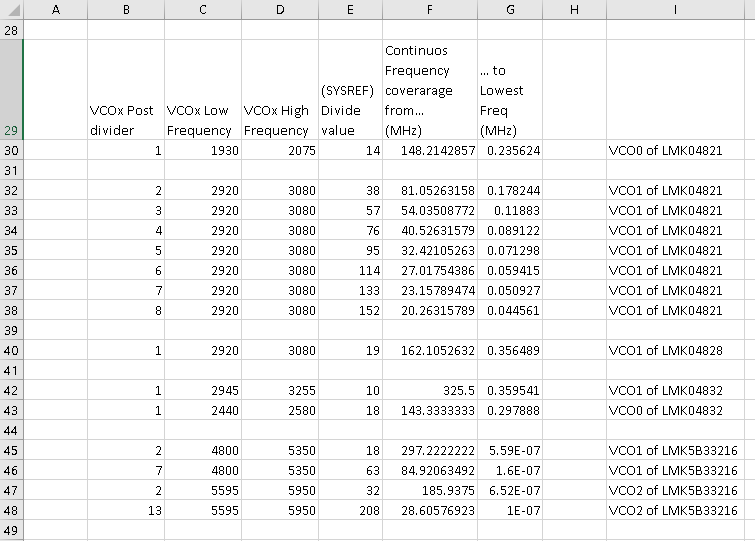

Other Parts Discussed in Thread: TMUX1108, LMP7721, DAC80501, DAC1282, DAC11001A, OPA828, DAC7664, LMK5C33216, LMK5B33216, LMK04832, LMK04828, LMK04826, LMK04821, SN74LVC1G132, SN74LVC1G74, CDCE6214

您好、德克萨斯州、

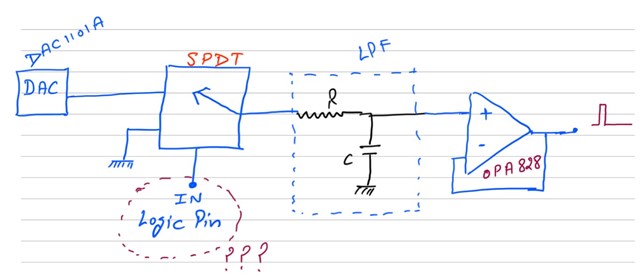

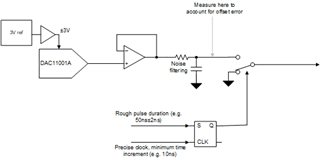

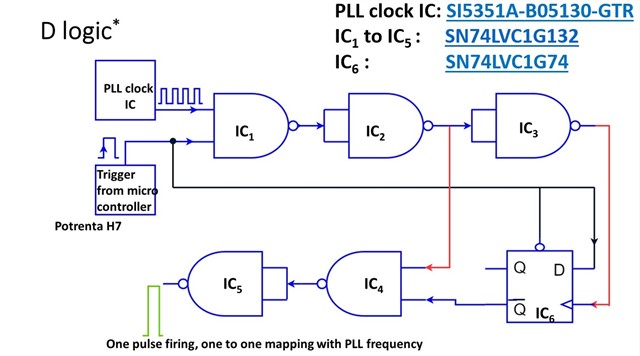

我希望在非常高的频率下生成超低噪声、低电压脉冲(10mV 峰间值、10ns 脉冲持续时间)。 我的要求是将脉冲振幅从10mV pp 变为2.5V pp、同时将脉宽从10nsec 变为100msec。

您能否建议使用分立式组件 IC 实现的可能高效解决方案? 该低电压、低振幅脉冲将通过 TMUX1108提供给存储器器件阵列(内部制造)。 使用 LMP7721多反馈增益可进一步感测输出电流(1nA 至1mA)。

请帮帮我。

谢谢

Deepak