Other Parts Discussed in Thread: CDCM61001

你好、

我使用 CDCM61001在电路板上生成200MHz 时钟。 我使用的基准是 ABM3B-25.000MHZ-10-1-U-T 您将找到时钟生成部分的原理图。

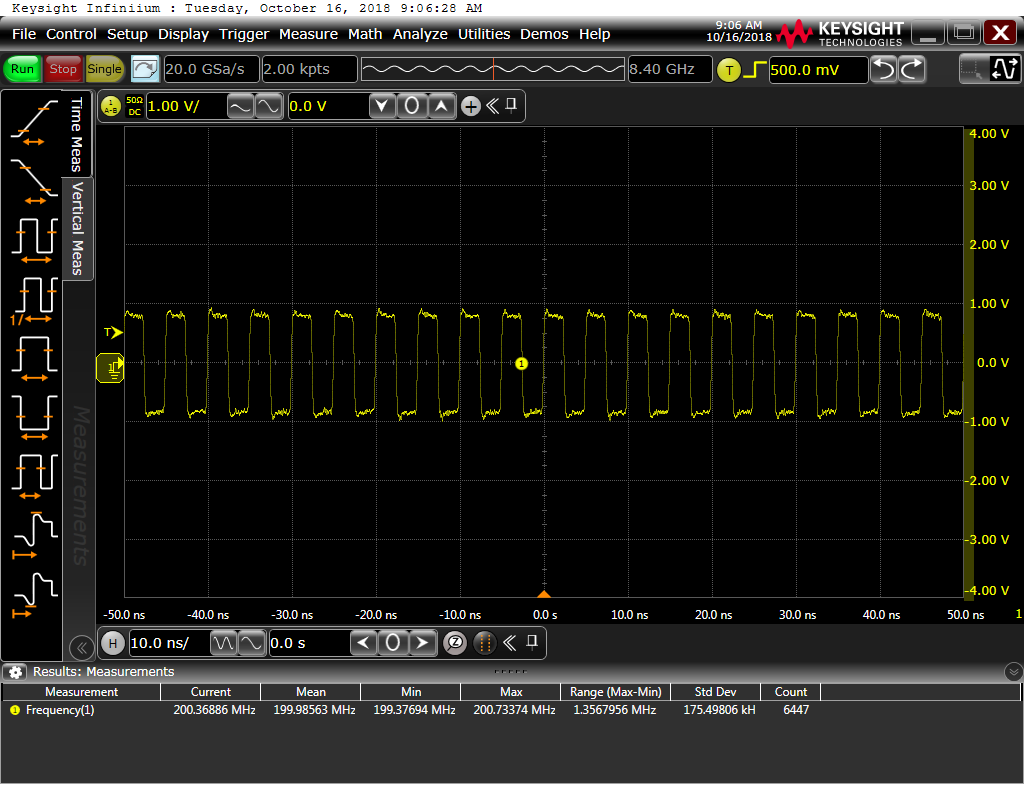

我测量的输出时钟似乎比我预期的稳定、跳频为130kHz、我怀疑第一个因素是我的参考时钟、其额定频率为10ppm。 我并不完全了解如何计算分流电容 C1、因此未能找到任何解释此设计选择的实用文档。 我也不确定我选择的 XO 是否可接受。

是否可以向我解释如何根据 CDCM61001的要求选择合适的基准振荡器和并联电容器? 如果能了解到我的时钟为什么不像预期的那么稳定、也会很感激。

谢谢你。

此致、

字符