Other Parts Discussed in Thread: LMX2571

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

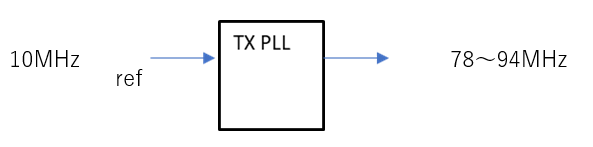

器件型号:LMX2571 大家好、

我的客户正在为 LMX2571的 TX 杂散而苦恼。

参考 LO 在10MHz +/- 80kHz 时具有~80dBc 杂散。

观察 PLL 输出(f0=78MHz–94MHz)、f0+/- 80kHz 杂散增加到60dBC (+20dBC)。

每次设置 R0寄存器时、杂散电平都会改变。

它会随机变为60dBC 或70dBC。

- 您能否告诉我 LO 杂散电平随 PLL 增加的可能原因?

- 杂散电平随 R0寄存器设置变化的可能原因是什么?

此致、

Itoh