Thread 中讨论的其他器件: LMX2592、 TIDA-01410

TI E2E 时钟论坛、

我之前曾与 Dean 进行过一次富有成效的对话,讨论我们要求从基于 DDR4的 DIMM 的 LVCMOS 时钟衍生出的1200MHz 差动输入源生成600MHz 时钟的要求。 我们成功地将1200MHz 时钟输入到 LMX2594 EVM 演示平台的 OSC 输入中。 但是、现在我们尝试在硬件平台上生成600MHz 时钟、结果并不相同。

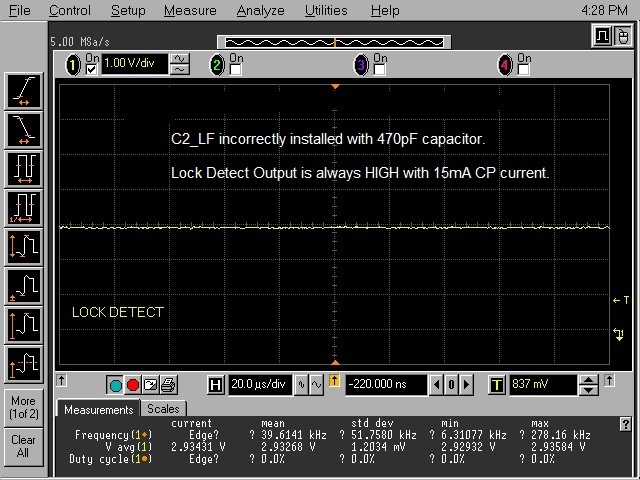

我们拥有一个非常干净的单片1200MHz 差动输入时钟、具有~ 2V P/P 摆幅。 我们将从 LMX2594获得非常干净的输出时钟、其1.2V P/P 摆幅需要传输到目标 FPGA 输入端的差分100 Ω 负载、射频输出强度设置为15。 我们的12GHz 示波器显示输出频率非常接近我们需要的600MHz、 但显然不够接近、因为我们无法像使用演示板工作台设置来确认确定性相位锁定那样在示波器快照上同步输入和输出时钟。 我怀疑环路滤波器可能是问题所在、因此我在监测 锁定检测信号时尝试了 TICsPro 中的所有电荷泵增益设置。 为我们提供恒定锁定指示的唯一设置是12mA 设置。 其他设置导致无锁定或间歇性锁定。 我意识到、即使是稳定的锁定检测输出 也是一个镇流器指示。 因此,我们显然很接近,但不够接近。

我们的硬件设计基于 LMX2592 EVM 用户手册中的参考设计。 我们在3.3V 电源轨和 LDO 输出上使用旁路电容器和大容量电容器时非常宽松。 输出电路使用数据表中建议的50欧姆方案、包括输出驱动器电源轨上的18nH 扼流圈。 环路滤波器与 TI 设计类似、但由于空间限制、我们使用的是0201元件、而不是 BOM 中指示的0603元件。 环路滤波器中的分立器件在 LMX2594的引脚35侧进行了紧密分组、并根据数据表布局建议将 C4_LF 放置在尽可能靠近引脚35的位置。 这与演示板不同、该演示板的环路滤波器分立器集中在演示板上 LMX2594的引脚12侧。 我希望这不是一个交易断路器。 我们使用的是具有所有环路滤波器互连的16层 PCB、但第1层上的引脚12连接除外、第2层上有一个完整的接地层。 与环路滤波器的引脚12连接通过第1层和第3层之间的通孔连接到滤波器分立器。 OSC 输入端接有一个100欧姆电阻器、后面接两个0.1 μ F 交流耦合电容器、如本参考设计中所示。 我们使用 EVM 控制模块和带10引脚连接器的 TICsPro 对 LMX2594进行编程。 使用10引脚接口中的以下线路:SDI、SCK、CSB、MuxOut、GND。 其余引脚为 NO_CONNECT。

当我们得到“锁定”指示时,LMX2594的编程如下:

频率= 1200MHz、倍频器= X1、前置 R = 24、R = 1、FPD = 50MHz、电荷泵增益= 12mA、包括分频= 4、N 分频器= 48、通道分频器= 16、RFoutA = 600MHz、VCO = 9600MHz。 VCO_PHASE_SYNC 框已选中。

我们非常感谢您为帮助我们调试该电路提供的反馈和指导。 我还注意到、2018年8月10日有一个有关 TICsPro 的更新、我希望明天下载并试用。

谢谢、

Ken