主题中讨论的其他器件: LMX2594、 LMK61E2

您好!,

在我的设计中、我使用一个 LMX04828B 为四个 LMK2594提供参考时钟和同步信号。 SYNC 信号用于对齐 四个 LMK2594的 SYSREF 时钟(4.8828125MHz)形式的 RFoutB。

但我发现、有时四个 SYSREF 时钟可以在上电后完全对齐、有时则不能。 您能帮我检查这个问题吗? 过程中可能会出现一些错误?

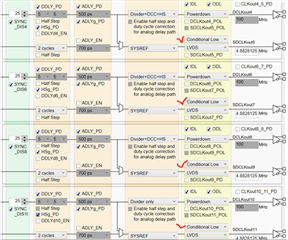

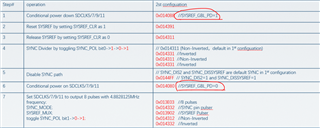

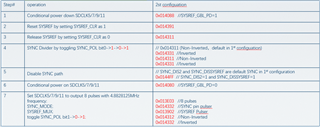

上电后、时钟配置的顺序为: LMK04828 1st configuration (basic configuration)-> LMK2594 configuration -> LMK04828 2st configuration (Generate Sync to LMX2594)

LMK04828 第一个 配置和 SDCLK5/7/9/11已 为4个 SYNC 信号准备就绪; DCLK2和 SDCLK3已提供给 FPGA

e2e.ti.com/.../LMK61E2_5F00_100M_5F00_SinglePLL_5F00_PD-25M_5F00_LMX2594_5F00_4-SYNC.tcs

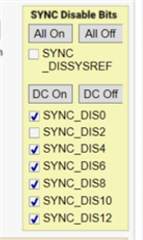

LMK04828 2st 配置:总共17个用红色标记的寄存器操作用于 使 SDCLK5/7/9/11输出8个连续脉冲、其中4.8828125Mhz 为4 LMX2594的 SYNC 信号

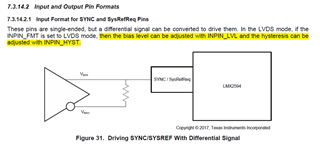

LMX2594的 INPIN_LVL 设置为 Vin、因为 Vin/4的默认值不会生效

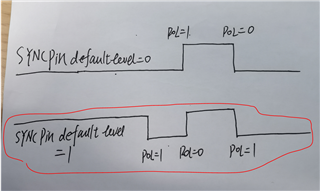

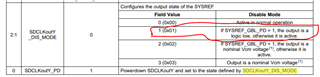

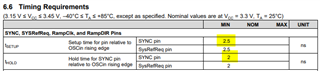

SDCLK5/7/9/11的输出格式为 LVDS、因此 LMX2594的同步格式根据下图进行设置。 C215和 C216已替换为0欧姆电阻器

提前感谢!!!

此致!

Jason