Other Parts Discussed in Thread: CDCE6214

您好!

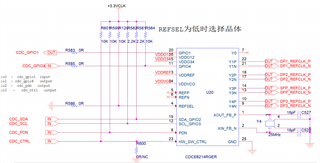

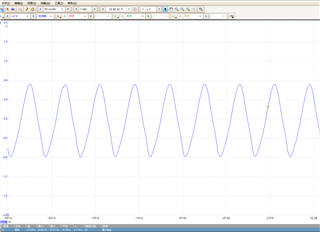

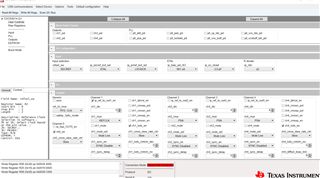

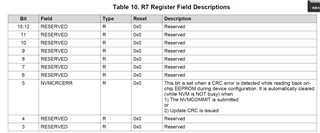

我的原理图 设计为使用25MHz 晶体 作为参考时钟、配置后、我们可以 从晶体引脚查看25MHz 波形。 但 PLL 无法锁定、因此我会将 Y0配置为输出、并源自 REFCLK。 但 CDCE6214的引脚7上没有任何信号。 我们还尝试从 REFCLK 配置 Y1源、但仍然无法获得任何结果。 那么、如何调试硬件呢? 晶振幅是否太小? 示波器显示峰峰值电压大约为1.5V,振幅足够了、但为什么我仍然无法获得 REFCLK?