大家好、

我们客户的一个问题、我将在下面转发、 请您提供一些故障排除建议

LMK04832使用 SDCLKOUT5输出两个 CMOS 时钟、并希望将时钟频率调整为1.25GHz 或2.5GHz。 在调试过程中发现、 在输出时钟超过11.1GHz 后、输出幅度开始衰减。 调整到1.25GHz 时、衰减已超过10dB。 在各种输出配置(例如 CMOS (norn/norm)\cmos (norm/inv)之间切换、并具有不同的衰减水平。 这可能是什么原因呢?

此致、

艾米·罗

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我们客户的一个问题、我将在下面转发、 请您提供一些故障排除建议

LMK04832使用 SDCLKOUT5输出两个 CMOS 时钟、并希望将时钟频率调整为1.25GHz 或2.5GHz。 在调试过程中发现、 在输出时钟超过11.1GHz 后、输出幅度开始衰减。 调整到1.25GHz 时、衰减已超过10dB。 在各种输出配置(例如 CMOS (norn/norm)\cmos (norm/inv)之间切换、并具有不同的衰减水平。 这可能是什么原因呢?

此致、

艾米·罗

Amy、

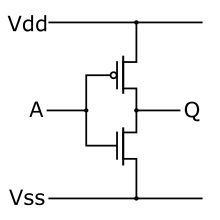

顾名思义、LVCMOS 输出缓冲器是低压互补 MOSFET 输出。 这意味着输出级源自采用"图腾柱"配置的 P 沟道和 N 沟道 MOSFET、具体请参阅下文。

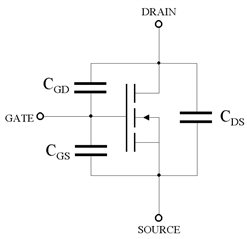

这些 MOSFET 在栅极到漏极、栅极到源极以及源极到漏极之间具有一些固有的寄生电容、它们会随着所施加 VGS 和 VDS 电压的变化而变化。 但 这些电容的数量级很容易在皮法范围内。

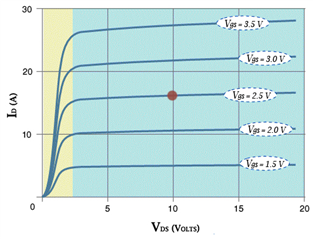

此外、每个 MOSFET 根据可在内部施加的栅源电势、具有一定的最大短路电流、MOSFET 会到达线性区域并开始像线性电阻一样工作。 该电流可能为几十 mA。

为了进行方便且大致正确的示例计算、假设5pF 是寄生电容、50mA 是 MOSFET 线性区域中可实现的短路电流-这相当接近 LMK04832的实际值。

现在、考虑一下1GHz 下的3.3V 正弦波。 以一个基本的导数,我们知道只有这个正弦波的最大转换率是2π* Vpk*F,在1GHz 时的最大转换率约为10V/ns。 顺便说一下、如果我们用5pF 和50mA、并假设 I = C * dV/dT、我们发现 dV/dT = 50mA/5pF = 10V/ns。 由于我们的输出电流在短路情况下受到漏源电压的限制、因此 我们的输出压摆率绝不可能比 3.3V 1GHz 正弦波更快。

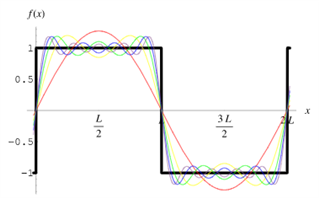

最后、请记住、要获得尖锐的方波、我们需要对 基波及其几个奇次谐波的傅里叶级数求和。

1GHz 的时候、我们能够在基频上得到一个合理的压摆率、但是3GHz、5GHz、7GHz 等的谐波都需要3倍、5倍、7倍的压摆率、才能获得具有相当振幅的正弦波。 我们无法提供足够的电流来在高阶谐波中实现类似的振幅、因此波形出现衰减、因为为其提供特征正方形形状的高阶谐波发生了衰减。 编辑:我记得在傅里叶级数求和中有一个1/n 的因子、所以实际上压摆率要求保持等效: 3GHz 处的三阶谐波振幅为基波的1/3、因此压摆率 应足以提供一个衰减范围以内的体面方波。 但是、寄生电容的阻抗在更高的频率下会急剧下降、并且形成寄生电容的短路 MOSFET 看起来像一个低通滤波器;因此、高阶谐 波的振幅会衰减20log (1/n)与方波的每个谐波所需的1/n。 在1GHz 以上时、我们仍然期望压摆率限制会影响振幅。

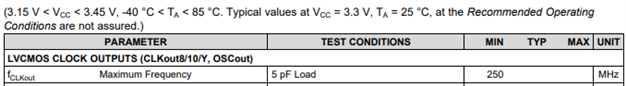

这就是为什么数据表列出 LVCMOS 的最大输出频率不小于250MHz 的原因之一-虽然我们可以合理地预计在250MHz 时有一个体面的方波、但在这个频率之上、我们期望逐渐过渡到衰减越来越多的正弦波。

还有其他原因、尤其是反射- CMOS 输出级的阻抗与有源级上 VDS 电压的函数关系可变(尤其是在从线性区域转换到饱和区域期间)、这使得频率更高的 CMOS 信号在没有 显著反射组件的情况下难以在接收器端接; 在连续运行中、这会产生驻波、容易破坏正常单调 CMOS 边沿。 通过精心设计的低电容 MOSFET 和 一些阻性阻尼来衰减反射有时可能会允许更高频率的 CMOS 信号、但通常仅在 MOSFET 电容可以更小的极低电压下、 或者在硅 ASIC 中、源与负载之间的距离(因此反射)可以忽略不计、并且电容相对于实际负载极低。

换句话说、不建议在 LMK04832上使用高于250MHz 的 LVCMOS 输出格式。

LMK04832上的其他输出格式使用双极晶体管代替 MOSFET、并且双极晶体管 在其有效使用模式下具有极低的寄生电容。 由于这种较低的电容、LVPECL 和 CML 等输出格式的衰减往往在较高频率下要小得多、即使总 电流负载较低、因为 C 的缩放比例远低于压摆率等式中的 I (几百毫微微法拉的低电容衰减大于电容衰减的10倍、 而驱动电流减少了2倍或3倍)。

此致、

Derek Payne