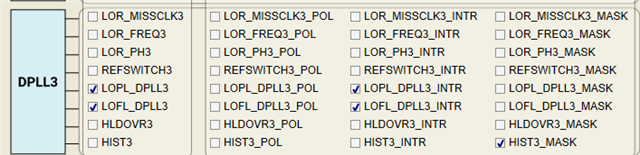

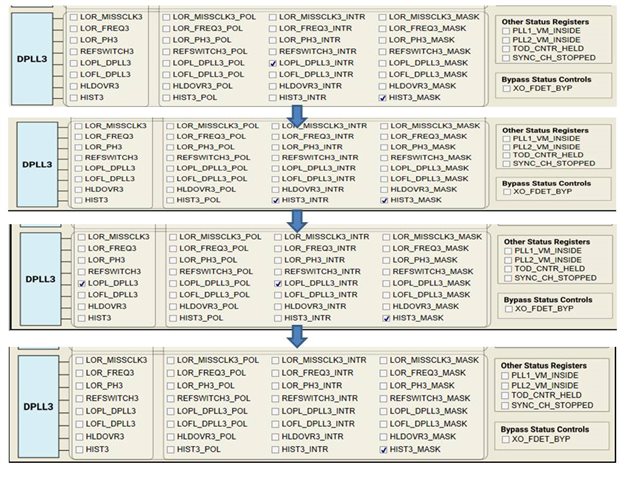

我想生成特定的时钟频率、在此过程中遇到一些问题。 我使用了随附的配置文件来在 TICS Pro 中配置 LMK。 加载 CONFIG 文件并读回状态位后、我发现 LOPL_DPLL3正在清除、并且在我执行"Clear Latched Bits">>"Read Status"时随机出现。 我附上了几个同样的例子。

为了进一步验证相位锁定、我尝试找到 LMK 器件生成的时钟信号与主时钟源生成的相同频率时钟信号之间的相位差、主时钟源也为 LMK 器件提供基准(REF1=10MHz、REF0=100MHz)。 可以观察到、两个时钟之间的相位差随时间而变化。

但当使用默认配置时、LMK 时钟和主时钟之间的相位差在写入时间内保持恒定、并且 LOPL_DPLL3 在读取状态时会被清除。

差分输出的预期 HD2幅值是多少?

e2e.ti.com/.../LMK5C33216-config-for-AFE-testing_2C00_-boost-on_2C00_-config1.tcs