主题中讨论的其他器件:CDCE913

【问题】

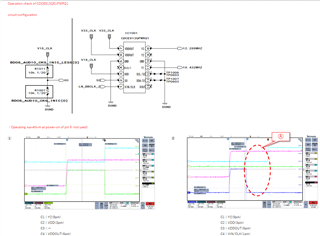

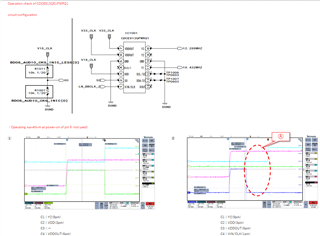

关于用Ⓐ虚圆・的部件①、当 Y2 (9引脚)从 H 下降到 L 时、电路板1的波形以 m Ω 为单位、电路板2的波形以 m Ω 为单位、而②的波形具有不同的时序。为什么? 蚊子?

・在(1)中的电路板1的波形中、我可以理解 Y2 (9引脚)从 H 到 L 的移动(当 VDD (3引脚)导通时更改为 L)、 但在(2)中电路板2的波形中、不清楚 Y2 (9引脚)的时序从 H 变为 L 的原因是这个时序。 请告诉我为什么是这样。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

【问题】

关于用Ⓐ虚圆・的部件①、当 Y2 (9引脚)从 H 下降到 L 时、电路板1的波形以 m Ω 为单位、电路板2的波形以 m Ω 为单位、而②的波形具有不同的时序。为什么? 蚊子?

・在(1)中的电路板1的波形中、我可以理解 Y2 (9引脚)从 H 到 L 的移动(当 VDD (3引脚)导通时更改为 L)、 但在(2)中电路板2的波形中、不清楚 Y2 (9引脚)的时序从 H 变为 L 的原因是这个时序。 请告诉我为什么是这样。

Satoru-San,

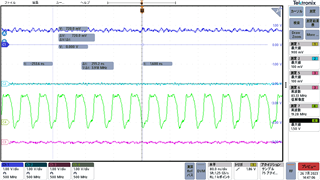

在第一部分、我看到 VDDOUT 升高、此时没有输出时钟、大约有80%的时间在上升:

在施加 VDDOUT 后、Y1或 Y3上升大约15%的时间。 这些时钟在应用 VDD 后保持高电平约650us、然后以正确的频率输出。

大约5%的时间、在施加 VDDOUT 后 Y1和 Y3都上升。 这些时钟 在应用 VDD 后保持高电平约650us、然后以正确的频率输出。

此外、无论时钟处于何种状态、在 VDD 上升时初始都会切换-请参阅以下内容:

在该过程中的任何部件期间、Y2会变为高电平。 我也会将我在这里得出的结果告知设计团队。

谢谢。

卡德姆

S·卡德姆

感谢您的评估。

以下是我希望确认的情况。

仍很容易理解为什么 Y2会被 VDDOUT 拉动并变为高电平。

从我发送的波形左侧可以看出、当 VDD 变为高电平时、Y2下降到 GND、因为器件的内部控制逻辑开始运行、所以我认为如果它像这样运行就没有问题。 不过、在右侧的波形中、Y2在 VDD 变为高电平之前下降到 GND。 这就是为什么在施加 VDD 之前(在控制逻辑开始工作之前) Y2从高电平变为低电平(GND)的原因。 我想知道为什么。

非常感谢。

Mr. Kadeem Samuel

感谢您与我们联系。

我们将使用电路板对其进行多次检查。

我们只有两个可用的板、但我们将尝试多次检查每个板。 我们将在确认后再次与您联系。

另外、我还有一个问题。 在650μs 我们发送的波形中、有一个说明振荡在2 μ s 后以正常频率发生、但是当振荡开始时、频率是否是从头开始设定的?

就我们而言、从 VDD 上升到时钟开始输出大约需要10ms。 (对于 Y1和 Y3)。

是否有任何可能的原因?

它所连接的电路是否有任何影响?

亲爱的哈德姆·塞缪尔。

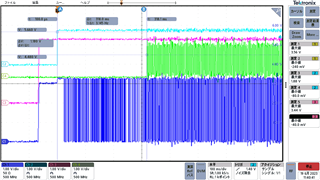

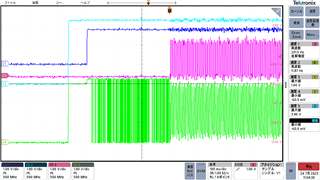

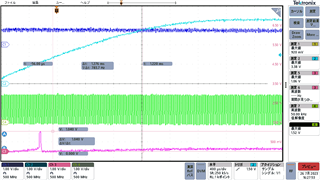

下面附加了上电时的波形。

C1:Y1 (18.432MHz)

C2:VDD (1.8V)

C3:VDDOUT (3.3V)

C4:CLKIN (19.2MHz LV-CMOS)

C1:(18.432MHz)输出一个未定义的频率、而不是设定的时钟频率、直到 C4 (19.2MHz)被输入。

虽然没有波形、Y3的12.288MHz 输出的行为方式也一样。

当 VDDOUT 上升时、Y2变为高电平、然后变为低电平并保持低电平。

(下面还提供了波形。) 每个通道与上述相同、只有 C1更改为 Y2。

您好,马岛山

当时钟输入(C4)处于低电平时、Y1和 Y3产生随机频率的行为很可能是由噪声导致的。 PLL 正在检测该噪声、以尝试创建一个频率。 我建议在 VDO 和 VDDO 之前打开输入时钟(C4)。 这可确保器件开启时、始终存在正确的输入时钟。 我还向设计人员确认了 XIN/CLK 具有失效防护、因此当时钟输入为高电平、但 VDD 和 VDDO 为低电平时不会出现问题。

对于 Y2的较高部分、这可能是由于时钟发生器的输入与您的电路的其他部分之间的耦合而发生的、这使我们难以在实验中复制该结果。 因此、我建议在 VDDO 之前为器件提供 VDD 来解决此问题。 这将强制 Y2保持在低电平 、因为它将由 VDD 控制和限制。 在器件的数据表中注明、我们不存在上电序列限制、因此请按此顺序尝试为输入供电1. 时钟输入(C4)、2. VDD (C2)、3. VDDO.(C3)

谢谢、如果您有任何其他问题、

您好、Yamabe 先生。

关于电源顺序、在与贵公司进行的 QA 清单交换中、我们回答说 VDD (1.8V)必须保持在 GND 电平、直到 VDDOUT (3.3V)达到特定的电压、否则会有大电流流向 VDDOUT 引脚。 因此、对于我们的产品、电源量级为 VDDOUT (3.3V) VDD (1.8V)。

现在无法更改。

此外、我被告知、如果 CLKIN 也处于 GND 电平、则在 PLL 锁定(GND 电平)之前不会输出时钟、

我已经对电路进行了配置、以便在 VDDOUT/VDD 电源打开后也可以为 CLKIN 计时、而这现在无法更改。

*该答案与我在贵公司的 QA 中到目前为止收到的答案不一致,这是否意味着 QA 列表中的答案是错误的?

您好,Majima-San,

请发送电子邮件至 k-yamabe@ti.com。

非常感谢

您好,Majima-San,

对于数据表中的上电序列、如果首先应用 VDDOUT、最好是将 VDD 保持在 GND、但 也可以先应用 VDD、然后应用 VDDOUT。 两个订单都适用于该器件。 您是否能够先测试提供 VDD 的器件、然后再测试 VDDOUT、以便我们确认问题?

您能告诉我是什么产生了 CLIKIN 吗? 在 CLIKIN 未通电时、我需要确认 CLKIN 是悬空还是接地。 这可能是导致输出问题的原因。

另外、我想知道为什么在两个电源之前无法打开 CLKIN? 此 E2E 博文讨论了电源配置、并建议在 VDDO 和 VDD 之前使用 CLKIN。 https://e2e.ti.com/support/clock-timing-group/clock-timing-internal/f/clock-timing---internal-forum/117389/cdce9xx-power-up-sequence?tisearch=e2e-sitesearch&keymatch=cdce9xx#

谢谢!

凯尔

Mr. Yamabe,

非常感谢您的帮助。

第一个 VDD 和 VDDOUT 的每个电源的序列目前无法更改。 此外,在更改后很难进行评估。

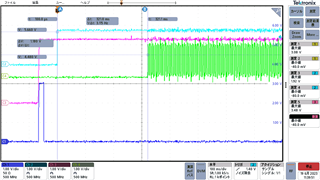

至于第二个、CLKIN、我将在将10kΩ Ω PD 电阻器连接到 CLKIN 引脚(引脚1)时向您发送测量的波形。

使用 PD 的情况和没有 PD 的情况之间没有特定的波形差异、Y1和 Y3的每个输出似乎都输出一个未定义的时钟频率、直到输入 CLKIN。

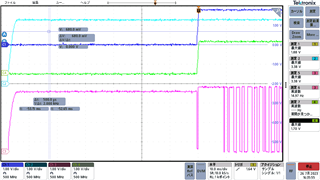

*同样地,在此板上,在 VDD 打开之前 y2总是从 H 变为 L。 (10个启动电源中的10倍)

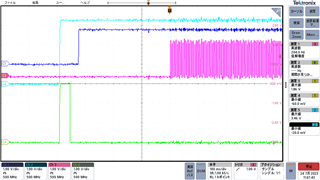

测量的通道配置如下所述。

C1:VDD

C2:VDDOUT

C3:CLKIN

C4:Y1 (第一个)、Y2 (第二个)、Y3 (第三个)

Mr. Yamabe,

非常感谢您的帮助。

当我在 VDD 和 VDDOUT 导通之前输入输入 CLK 时、我发现大约0.7V 电压流入 VDD 电源引脚。

我们的产品不接受此状态、因为 VDD 电源(1.8V)也用于其他器件。

因此、我们无法在打开电源之前输入 CLK。

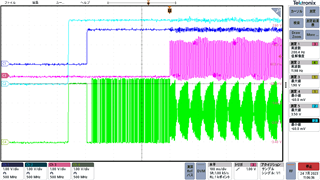

我们将在此时向您发送波形。

VDDOUT 和 VDD 未开启的波形(0.7V 流入 VDD 电源引脚...) 并且发现 CLK 未输出到 Y1。

同时还发送波形。

此外、在 VDD 和 VDDOUT 电源开启而没有 CLKIN 的情况下、当 VDD 开启时、CLKIN 会进入高电平、然后输出无限频率。

同时还发送波形。

测量通道如下所示。

C1:VDD

C2:VDDOUT

C3:Y1

C4:CLKIN (1引脚)

Yamanobe 先生。

非常感谢您的帮助。

我知道当 CLKIN 是第一个输入时、它会按预期工作、除了大约0.7V 流入 VDD。

但是、对于整个产品而言、流入 VDD 是不可接受的。 另外、由于整体产品设计的原因、无法早于 VDD 和 VDDOUT 电源输入 CLKIN、这是最后一个。 (因为 CLKIN 由电源 IC 供电:PMIC)

当 CLKIN 为 GND 且 IC 的 VDD 和 VDDOUT 电源输入时、是否可以避免以未定义的频率向输出时钟输出 CLK?

Majima-San,

我们的团队讨论了 如何在 CDCE913的 VDD 引脚上添加肖特基二极管、因此即使 VDD 上的电压升至0.7V、也不允许电流流向其他系统。 但根据我的理解,这也不是一个选项。

为了避免以未定义的频率输出 CLK、由于其他控制引脚配置设置为关闭所有输出-如果在启动时使用了不同的控制引脚设置(例如、S2=1、S1和 S0无关紧要)、输出是否全部关闭? 是否有 GPIO 可用于然后更改 S0/S1/S2状态?