大家好、

我们在定制 PCB 板中使用您的组件 LMX1204。 我们在 SPI 编程信号(SCLK、SDO、SDI 和 CS)中遇到了一些困难。

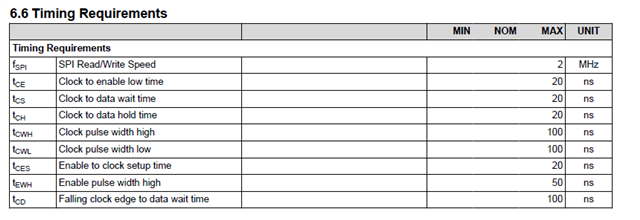

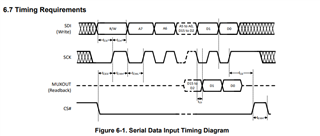

在下面说明的数据表的图6-1中、定义了 SPI (也在数据表的"此器件的建议 SPI 设置是 CPOL=0和 CPHA=0。"图的后面文本中。 这意味着、如下图所示、CS#之后的 SCLK 的第一个边沿为上升沿、且在没有执行任何 SPI 周期时、时钟引脚为低电平。 此外、SDI 和 SDO 上的数据在时钟的上升沿被采样、而在下降沿被"改变"。

由于我们无法在定制 PCB 上对 LMX1204进行编程、因此我们会进行不同的分析、而且由于我们还购买了 LMX1204评估板、因此我们会在评估板上提供的引脚上测量 SDI、SCLK 和 CS#。

我将在下图中展示该电路板上的示波器信号。

由于 SCLK 的第一个边沿在 CS#之后下降、CPOL 看起来不是0而是1。 我将为您进行缩放:

黄色曲线为 CS、紫色为 SCLK、蓝色为 SDI。

我们使用 TICS PRO SW 界面对 LMX1204评估板进行编程。

有人能解释一下为什么数据表和评估板上使用的运行模式之间存在这样的差异?

非常感谢。

此致!