主题中讨论的其他器件: LMK00301

大家好、

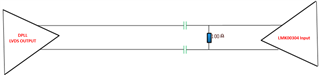

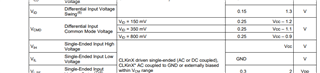

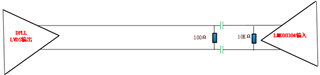

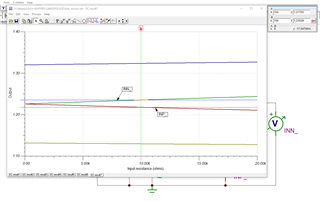

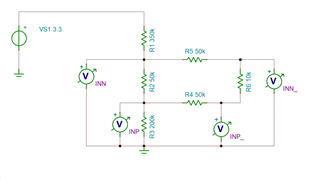

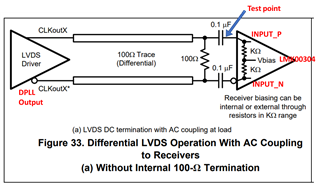

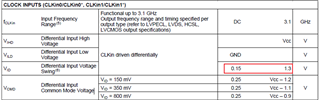

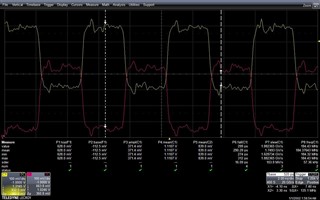

客户当前项目需要使用 LMK00304时钟缓冲器。 电路设计如图1所示。 在测试过程中、发现交流耦合时、输入时钟摆幅不满足差分输入0.15V 的规格要求。 使用万用表进行的测量表明、缓冲器输出的共模电压存在一定的差异(CM_P:1.08V;CM_N:1.35V)。 您能否帮助确定 LMK00304输入中 PN 共模不平衡的具体原因、以及它是否可以在此类条件下正常使用? 谢谢!

图1:电路设计

图2:LMK00304输入时钟摆幅规格

图3:LMK00304输入侧波形的实际测试

Br

艾达里安