主题中讨论的其他器件:AFE8030

大家好、

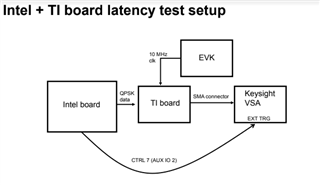

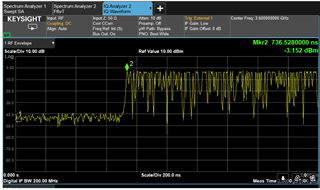

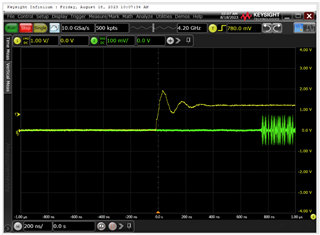

在我们测试从 FPGA 到 TI 的数据路径延迟时、我们看到了~740ns 的高延迟。测试过程如下

我们是从 Intel 主板触发信号、同时触发 VSA 触发输入、因此我们看到从 FPGA 到 TI 的延迟为~740ns。

我们还使用示波器进行了测试、还获得了~740ns 的相同结果、即 TI AFE8030的预期行为。 我们测试是否正确?

我们还面临着 与10MHz SPI 时钟的单次事务的 SPI 事务的问题,我们得到~96us 延迟。 我们可以向 TI 电路板提供的最大时钟是多少?