主题中讨论的其他器件: LMX2595

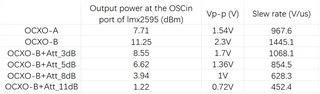

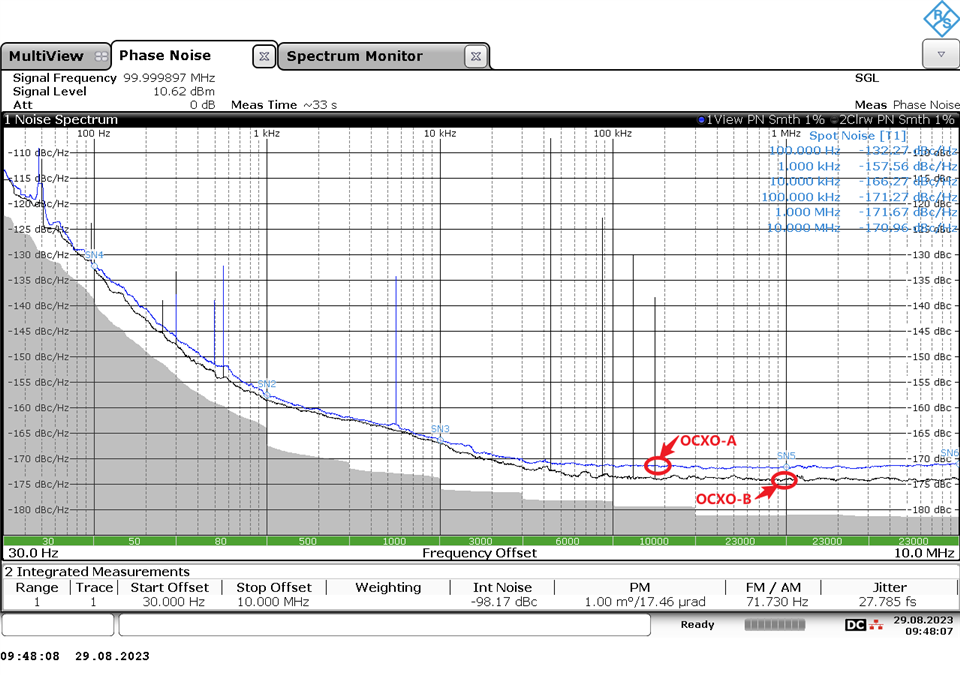

你好。 我们将使用 两个100MHz OCXO 测试 LMX2595EVM。 参考时钟 的频率为100 MHz、并且启用了 LMX2595EVM 的 OSC_DI倍 频器。

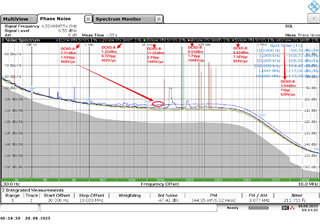

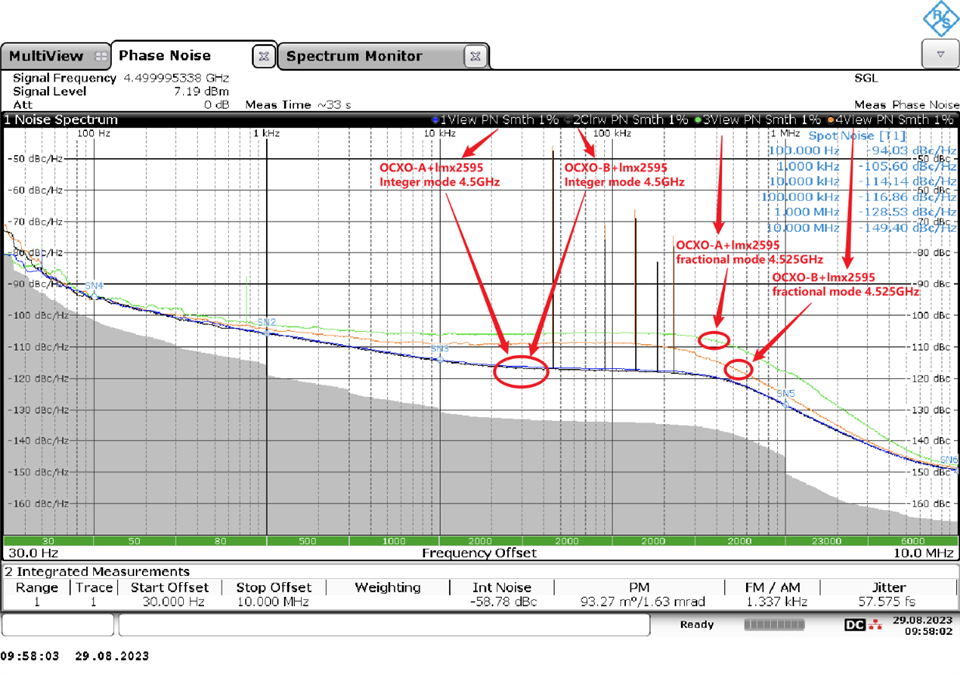

我们发现、当 LMX2595处于整数模式且两个 OCXO 用作基准时钟源时、在高于1kHz 的频率偏移处测量的 LMX2595相位噪声基本相同。 但是、在分数模式下、启用 Σ-Δ 调制器会导致两个源的相位噪声降低、但会下降到不同的程度。 从结果中可以看出、 根据所使用的基准源、Σ-Δ 调制器引入不同级别的相位噪声、所添加的相位噪声较少、从而获得更好的基准源。 我们希望确认 Σ-Δ 调制器是否确实具有此特性。

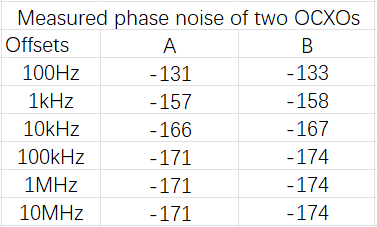

两个 OCXO 和 LMX2595测量的相位噪声如下。

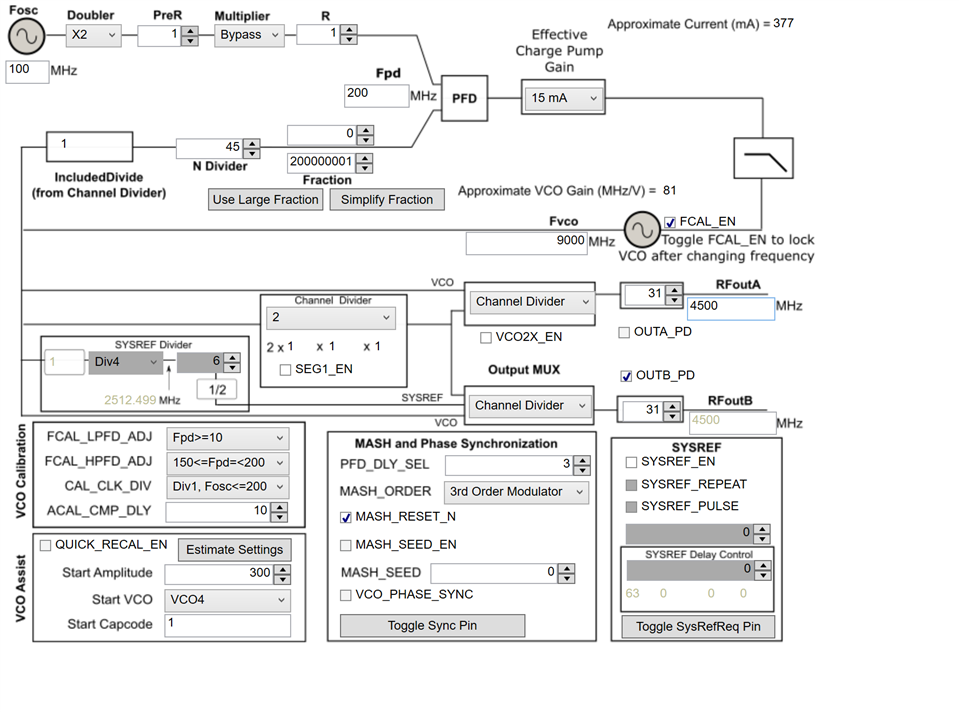

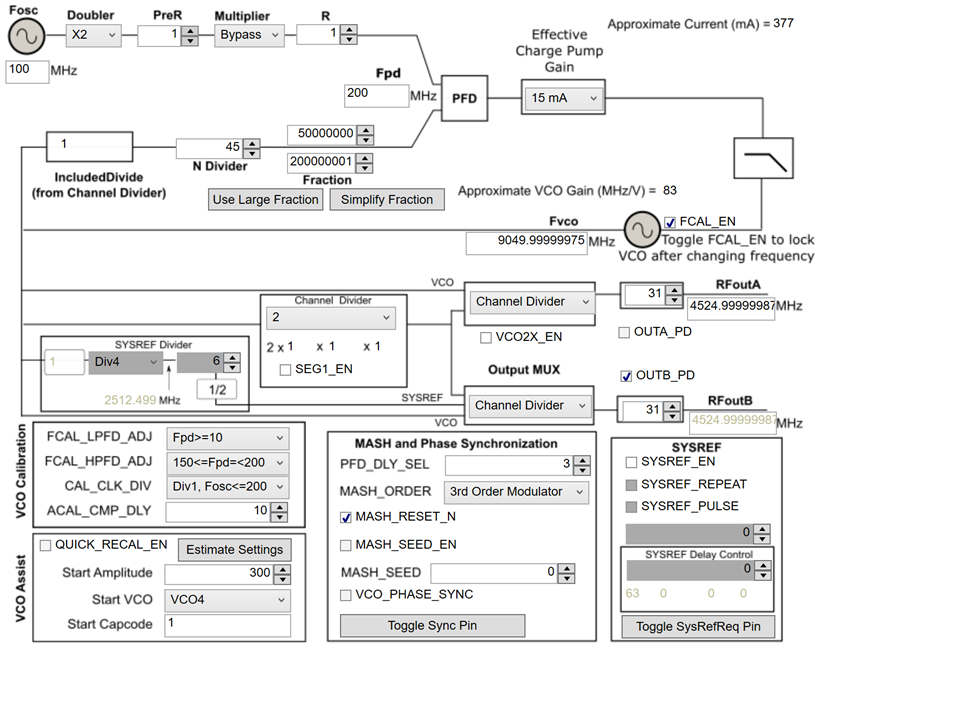

整数和分数模式下 LMX2595的 TICS Pro 配置如下图所示。