主题中讨论的其他器件:LMK05318B、 LMK5B33216

我有一个10 MHz 时钟信号、我正在尝试创建一个具有已知相位偏移的频率同步输出。

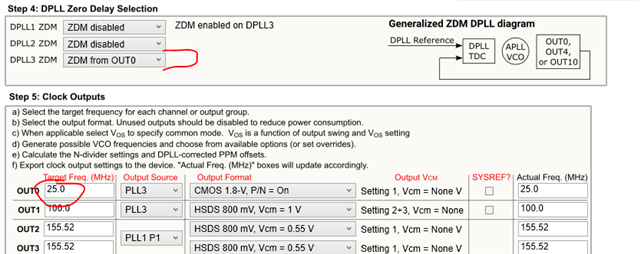

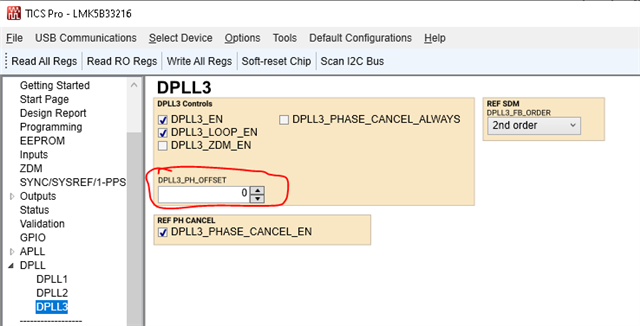

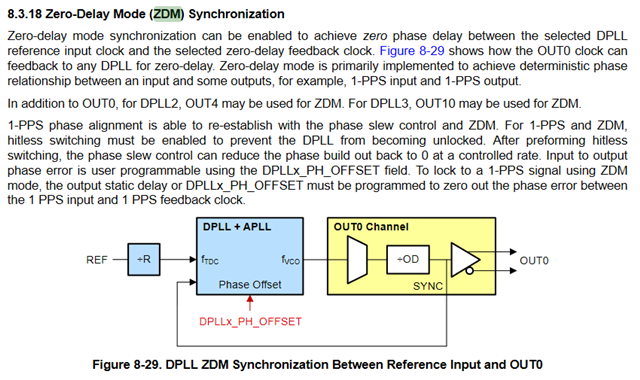

我通过启用 DPLL 将10 MHz 输入连接到 PRIREF、并使用 APLL1在 OUT0上提供输出。 我尝试使用 DPLL_REF_SYNC_PH_OFFSET 寄存器调整输出的相位。 我有三个问题需要解答。

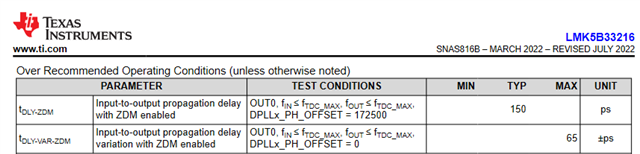

首先、如果不通过 DPLL_REF_SYNC_PH_OFFSET 施加任何偏移、我可以预期、如果 OUT0上的输出锁相到 PRIREF 上的输入、然后在5318上点击软复位就不会影响输入和输出之间的相位偏移。 然而、每次我遇到软复位并且 PLL 重新获得锁定时、输出都会稳定到相对于输入的随机相位偏移。 这是预期行为吗?如果是、为什么? 这是配置问题吗?

其次、可以 按我正在尝试的方式使用 DPLL_REF_SYNC_PH_OFFSET 寄存器吗? 换句话说、您是否可以使用该寄存器在5318的输入和输出之间创建已知的相位偏移?

第三、假设上一个问题的答案是肯定的、是否可以实时进行此类调整? 试验评估板时、 只有在芯片执行软复位时才会读取 DPLL_REF_SYNC_PH_OFFSET 寄存器的任何更改。 似乎器件应在所做的更改时读取寄存器更改、而不需要复位芯片。 是这样吗?

提前感谢大家能够提供的任何帮助。

乔什·怀特