大家好、

我的客户正在考虑将此器件用于单稳工作模式、并且对 TRIG 输入有疑问。

在下面的 E2E 主题中、规定 TRIG 输入脉冲宽度必须大于100ns。 我的客户想知道是否有上升/下降时间规格或压摆率规格。

此致、

大桥

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的大桥三、

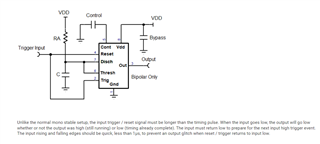

我唯一能找到的关于上升/下降时间的指导就在您引用的同一个常见问题解答帖子中。 它是一种略有不同的单稳配置、其中触发引脚连接到 RESET。 在此配置中、建议的上升/下降时间为1μs 或更短。

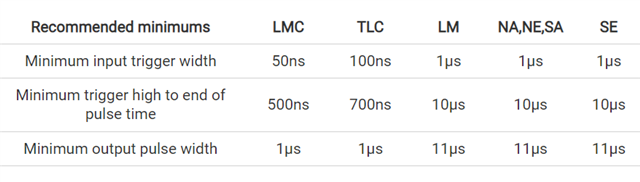

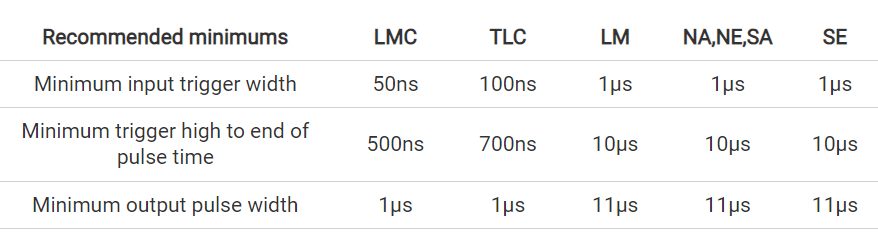

您可以遵循本指南作为 单稳触发器输入的最大上升/下降时间。 但是、 根据 所需的频率、上升/下降时间可能需要快得多、因为最小单稳态脉冲宽度也为 1μs。 上升/下降时间 必须适应最小100ns 的低触发 宽度以及到脉冲时间结束的最小700ns 的高触发宽度。

此致、

扎赫

尊敬的 Zach:

感谢您的支持。 我的客户还有其他问题。

我的客户听说、 当向逻辑 IC 输入慢速信号时、如果超过输入阈值、逻辑 IC 会工作并瞬间消耗电流、从而使电源 GND 振荡。 我听说输出将会不稳定和振荡。 TLC555是否发生了同样的情况? 或者、如果触发信号由于噪声而闪烁、那么如果在短时间内多次超过输入阈值、操作是否会变得不稳定?

此致、

大桥

尊敬的 大桥三、

1.) 在这种情况下、上升/下降时间的定义是什么?

通常、上升/下降时间定义为脉冲上升或下降到 稳态值的10%到90%之间所需的时间。 上升/下降时间 必须适应最小100ns 的低触发 宽度以及到脉冲时间结束的最小700ns 的高触发宽度。

2.) 如果上升/下降时间不符合建议值、会发生什么情况? 会振荡吗?

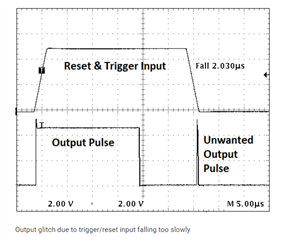

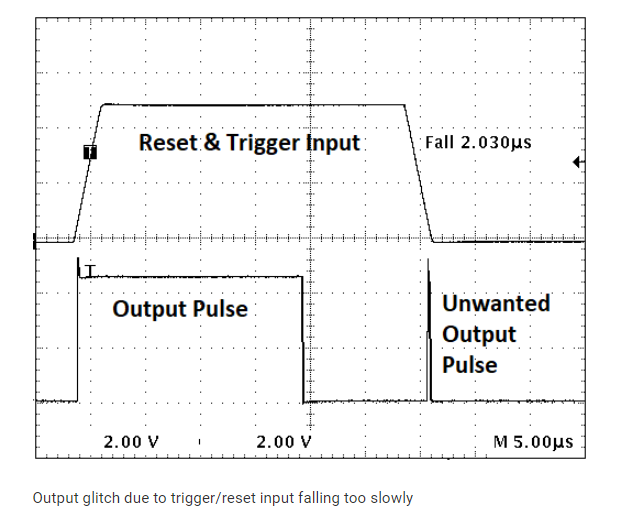

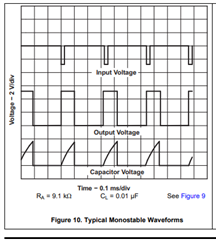

在我上一篇文章所示的配置中、如果下降时间超过1μs、则可能会出现如下所示的无用输出脉冲。 输出未振荡。

在典型的单稳配置中、如果触发在脉冲结束前未恢复到高电平、则输出将延长、直到触发变为高电平。 关键技术规格是触发信号为高电平或低电平的时间长度、如表中所示。 您可以将上升/下降时间设计为适应 所需 计时频率所需的必要触发宽度。

3.) 我的客户听说、 当向逻辑 IC 输入慢速信号时、如果超过输入阈值、逻辑 IC 会工作并瞬间消耗电流、从而使电源 GND 振荡。 我听说输出将会不稳定和振荡。 TLC555是否发生了同样的情况?

您能否指定您指的是哪种逻辑 IC? 这是另外一个555计时器吗? 阈值引脚处的电压斜坡速度由外部 RC 网络决定。 当 RC 值较大时、此电压斜坡可能非常慢。 一旦阈值引脚斜升至高于 VCC 的2/3、只要 TRIGGER 引脚处于高电平至少700ns、输出脉冲就会复位。 此 操作 会对电容器电压进行放电、对于555计时器的功能至关重要。 确保您的器件在 PCB 布局中具有良好的低阻抗接地连接、能够从该电容器放电中吸收电流。 输出未振荡。

4.) 或者、如果触发信号由于噪声而闪烁、那么如果在短时间内多次超过输入阈值、操作是否会变得不稳定?

触发信号必须保持高电平至少700ns、器件才能识别触发信号。 为确保单稳工作正常、您必须确保在脉冲宽度结束之前触发器处于高电平至少700ns。 如果触发器在700ns 内不为高电平、则输出将延长、直到 触发器变为高电平。 触发输入 级别- 敏感而不是边沿敏感。

555计时器具有电平敏感特性、因为内部触发器和阈值比较器连接到内部触发器。 为了触发输出脉冲的复位、阈值引脚必须高于 VCC 的2/3、并且触发引脚必须高于 VCC 的1/3。 如果输出脉冲被触发为高电平、在输出可以再次被复位前、外部电容器必须被充电至 VCC 的2/3。 输出未振荡。

此致、

扎赫