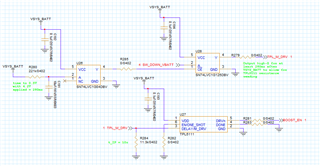

主题中讨论的其他器件: SN74LVC1G125、SN74LVC1G04 、

我的用例为:

EN/ONE_SHOT = GND (单冲模式)。 TPL5111 M_DRV 通过切换开关保持高电平(非瞬时)、因此 DRVn 始终为高电平(保持负载开关启用以为系统供电)。 切换开关时、M_DRV 将变为低电平、定时器周期结束后、DRVn 将变为低电平(关闭负载开关)。 实际上、这是一个延迟关断电路。

我担心的是计时器转换时间、如果 M_DRV 在引导时保持高电平、或在转换时间 t_Rext 结束前变为高电平、这会对存储的计时器间隔周期产生什么影响?