主题中讨论的其他器件: LMK04906、 、CODELOADER、 USB2ANY

大家好。

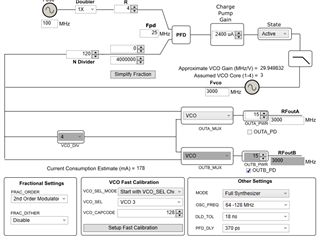

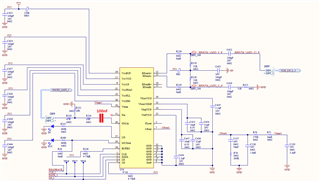

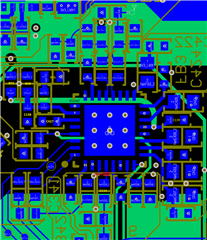

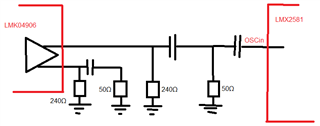

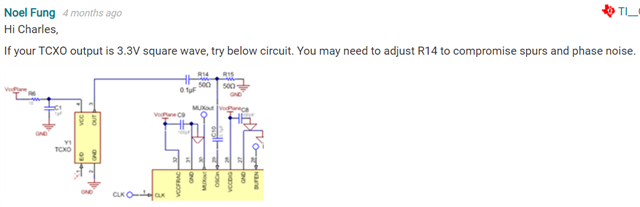

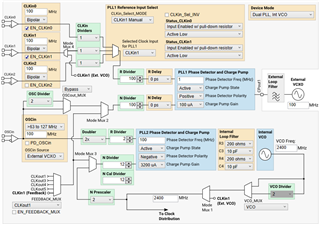

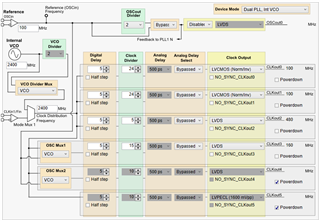

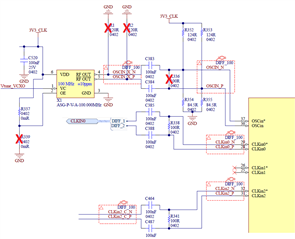

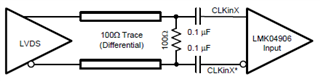

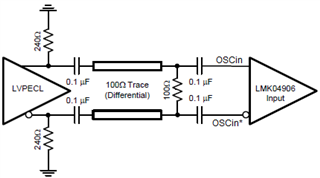

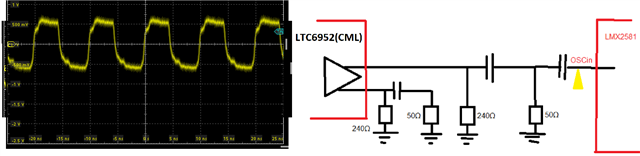

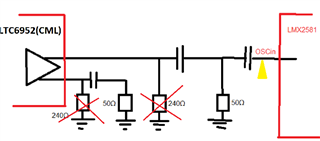

在项目中、我们在一个 PCB 中使用两个 LMX2581、两者 的电路、作用和布局都非常相似。 另一方面、布局与 EVM 板没有显著差异。 这两种信号都具有由 LMK04906用频率100MHz 分配的 OSCin 信号、振幅 约为1、6Vpp (在 OSCin 引脚上)、是看起来不错的子波。 说明电路、环路滤波器部分与数据表中的9.2.2.2章节类似。 我们的目标是在每个芯片的一个输出上实现1GHz (例如1000G 和1500G)的输出频率。 我们使用 TICS Pro 生成寄存器值、并通过 SPI 使用 Raspberry Pi 对其进行写入。 LMX2581的编程序列包含:使用复位位对 R5进行编程、在每个寄存器之间以大约500us 的延迟对寄存器 R15-R0进行编程、并在大约160ms 后再次对 R0进行编程。 每次芯片按顺序编程:LMK、LMX (1)、LMX (2)、这样我就能在两个 LMX 上观察 beachvior、因为它们的配置相同。 区别在于:LMX (1)在 LMK 附近的 OSC 信号中具有交流耦合电容器、而 LMX (2)在 OSCin 引脚前面有额外的电容器(如 EVM 板那样具有电路化)。 LMK04906提供的时钟仍然存在、但芯片位于同一电路板上。

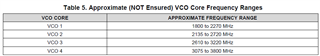

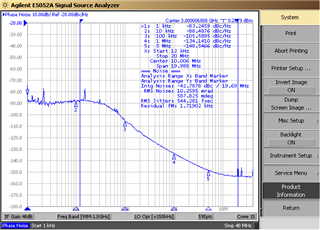

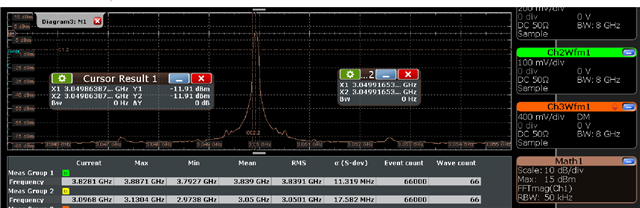

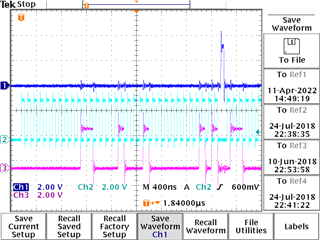

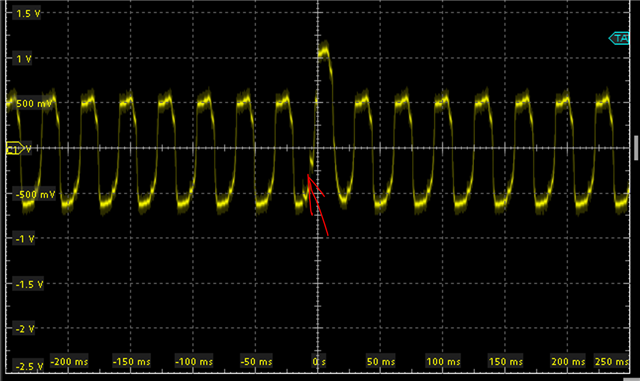

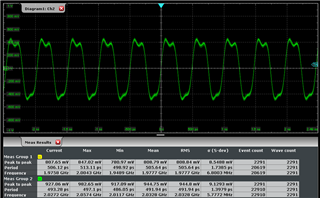

我 曾尝试达到目标输出频率、但当它无法成功时、我尝试获取任何设置频率并获取锁定状态。 我试过几十种配置、无法达到正确的频率、 在 LD 引脚上获得"DLD & VTUNE GOOD"。 在某些情况下、器件会提供最大 VCO 频率、最终除以 VCO_DIV。 在其他配置中、频率错误、但与 VCO 的极端频率 不同、在采用同一配置的两个编程序列之间、频率有时会有所不同。 在某些配置中、器件提供的频率与配置不同(例如:SET 1900m、GET 2200M 或2050M)、但我在 LD 引脚上得到"VTUNE"(好信号:))、Vtune 电压稳定在1.26V 左右、这意味着(正如我从其他主题中读出的)电压调谐正常、 模拟部分锁死了、但能拿到"DLD"(数字锁检测)。 在一些配置中、我得到1810MHz、当设置1805MHz 时、什么看起来不错、但发生任何锁定、偏差为3MHz、并将设置频率更改为例如1750MHz、我得到1900MHz。 现在、我希望在 LMX2581的 OSCin 引脚上有额外的电容器、因为它始终在 LD 上设置"OSCin SET"、当 LMX 没有额外的电容器时、有时会设置它。 我试图:改变 VCO (通过强制)、泵增益、分频器和乘法器组合、VCO_CAPCODE 值、FPD 频率、更改编程序列(例如、添加3次编程 R0、有时会改变效果)等、但无法实现。 我认为最高 FPD 频率更好(如数据表中所述)但并不总是如此。 我曾尝试使用 LD 引脚作为"R/2"或"R/4"、但在某些情况下、我在 LD 引脚上没有获得此信号。 输出频率的偏差约为1 -3MHz。 有时、我 在编程后一小部分秒内看到频率是适当的、并变为不正确。 我对诊断功能有一些疑问、当然主要问题是:

1.如何获得正确的频率和锁定? 我如何对其进行调试或诊断?

2.我可以解释 LD 引脚上的"OSCin Det"是因为 OSCin 信号是正确的吗? 这意味着我无法这样做。

3、如何检查4个重要事项是否正确:编程、输入信号、电压锁、数字锁?

我认为这是数字(相位检测器)问题、但正如我认为如果 VTUNE 电压是正确的、我们只需要相位检测、但我不知道如何诊断/调试它。

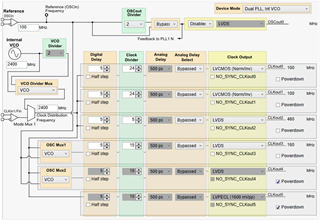

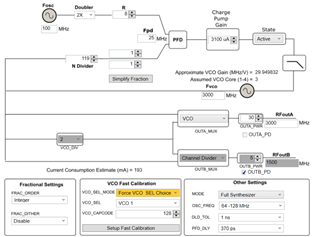

现在我回到起始点(数据表中的9.2.2.2章节配置)。 按如下所示设置配置、并获得如下频率(在 LMX2581上、在 OSCin 引脚上使用额外的电容器、因为如果没有该电容器、第二个 LMX 会提供2800MHz)、LD 上的"VTUNE"为高电平、Vtune 电压为1、23V。

非常感谢您的帮助。

此致