您好!

我们正在使用 cdce62002将13MHz 的基准时钟转换为204.8MHz 的时钟。

以下是我们使用的配置。

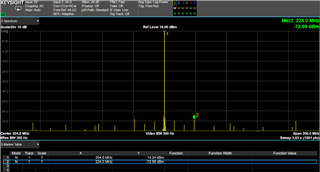

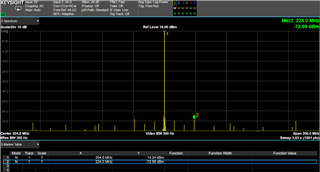

问题是、我们在输出端遇到许多杂散(请参阅所附的频谱分析仪屏幕截图)。 这些值非常低、但对于我们的应用来说还不够低...

我的问题:你能不能建议其他配置,它可以降低这些杂散的水平? 或使其相对于载波的偏移较高(即将其移开、以便我们可以滤除 uisng 带通滤波器)

谢谢

丹

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们正在使用 cdce62002将13MHz 的基准时钟转换为204.8MHz 的时钟。

以下是我们使用的配置。

问题是、我们在输出端遇到许多杂散(请参阅所附的频谱分析仪屏幕截图)。 这些值非常低、但对于我们的应用来说还不够低...

我的问题:你能不能建议其他配置,它可以降低这些杂散的水平? 或使其相对于载波的偏移较高(即将其移开、以便我们可以滤除 uisng 带通滤波器)

谢谢

丹

Dan、

我查看的结果仅适用于载波的15 MHz 偏移(我们的仪器仅以载波为中心捕获到15 MHz、否则必须更改中心频率)。

环路滤波器和 PLL 设置的任何配置都不会产生足够的杂散抑制、尤其是不低于-90dBc。

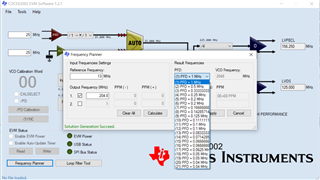

对于其他测试、您可以使用内置频率规划器、输入基准和输出频率、单击"Calculate"、然后在 PFD 时从 21个可能选项中选择一个:

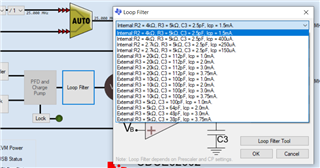

选择 PFD 设置后、可以使用4个完全内部设置或多个外部设置来修改环路滤波器、从而更改 C3和 R3值:

谢谢。

卡德姆