"你是什么人?

我想问您一个问题。 我们正在设计双环路模式的 LMK04832-SP。我们对该模式进行了一些测试、我们注意到 PLL2单环路模式比双环路模式的性能更好。 我们正在使用 PLLatinum、我们在 PLLatinum、双模和单模下完成所有测试、我们可以使用 PLLatinum 对数据表中的 PLL2单环路性能进行仿真。 请参见下图。

-------------------------------------------------------------------------------------------------------------------------

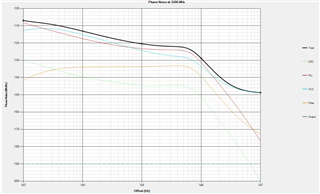

在3200Mhz pll2单模式下仿真数据表性能

-------------------------------------------------------------------------------------------------------------------

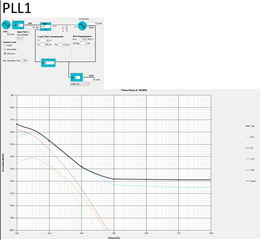

1600MHz 时的双路模式性能

在我的双模情况中、我们在 PLL1的输入端有一个100Mhz 的 XO、PLL2的输入端是 PLL1的输出端。

-------------------------------------------------------------------------------------------------------------------

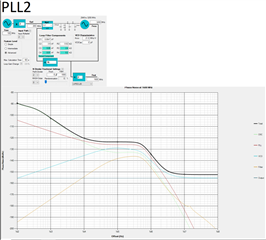

1600MHz 时的 PLL2单路模块性能

在我的 PLL2单模情况中、我在 PLL2的输入端有一个100Mhz 的 XO。

-------------------------------------------------------------------------------------------------------------------

我们在数据表中已阅读到、双环路 PLL 架构应提供最低的抖动性能、但根据我们的仿真、我们获得了相反的结果。

你知道为什么会这样吗? 我们想了解单模性能为什么优于双模。

好的。

M·科森蒂诺