主题中讨论的其他器件: LMX2581

我们正在使用多个 LMX2572 PLL、我们希望每个 PLL 之间具有相位相干、还希望参考频率(例如 PLL 的输入频率)、这些频率都与 PLL 的零相位点相位对齐。

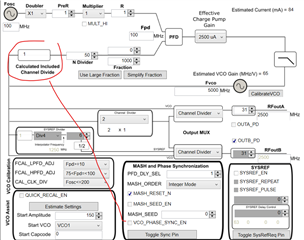

所需的工作频率是2.4GHz 至2.5GHz 之间的 ISM 频带。 意外的是、如果没有通道分频器就无法实现这一点。 如数据表(页17/90)中所述:

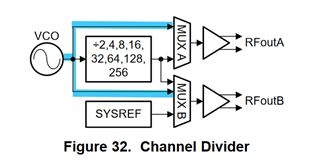

"要低于3.2GHz 的 VCO 下限、可以使用通道分频器。" 理想情况下、由于我们只需要使用整数 PLL (例如、100MHz *(N = 24)= 2、4GHz)、因此我们希望绕过此过程。

问题1:是否可以在没有通道分频器的情况下实现该值、数据表中没有该值?

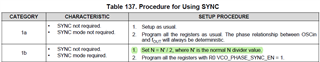

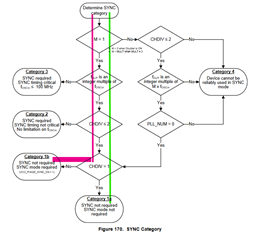

根据数据表的建议(第67/90页):

红色路径:我们设置 CHDIV = 0 (为此公式给出2的通道分频器值)

1.(PLL_N = 50、PLL_NUM = 0且 PLL_DEN = 1000)更改为了结果(2、5GHz)-->通道1 (黄色)

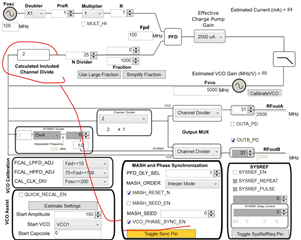

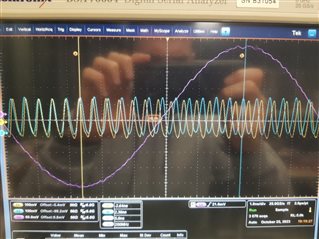

这可以正常工作、但同步模式未按预期工作。 我们在复位后根据建议将寄存器 R0 (偏移:00h)设置为(2118h)、然后设置为(6118h)。 通过此设置(VCO_PHASE_SYNC_EN = 1)

问题2:如何精确地激活 SYNC 模式、而不仅仅是设置该位? 我们得到的是 BIZAR 行为、如跳频和振幅、因此没有设置该位是不可靠的频率。

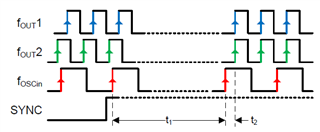

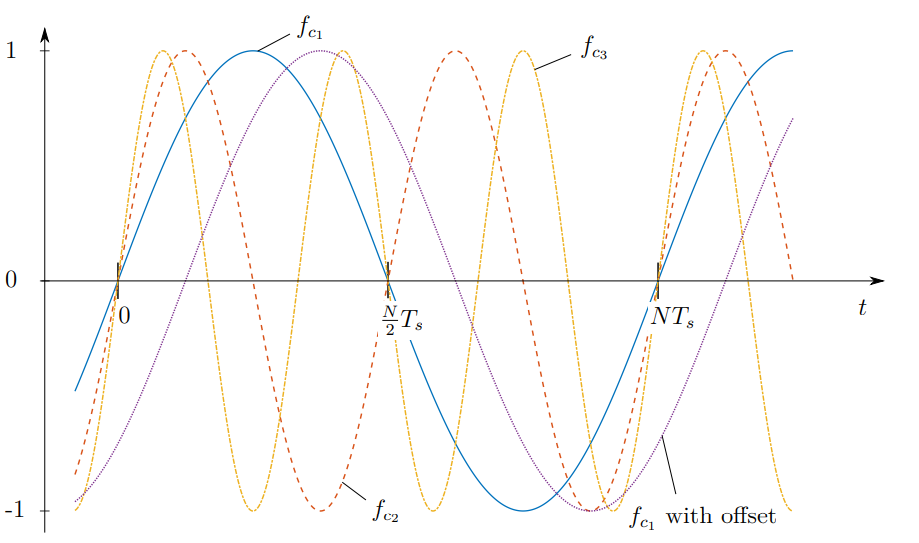

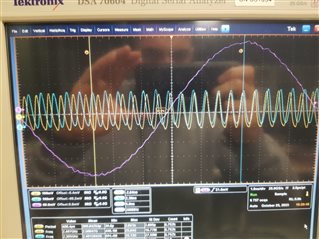

相反、由于整数 PLL 的性质、我们得到了基准频率的同步行为、此行为只有在以偏移重新加电后才能重现。 请查看以下图片:

我们认为、这可能是由通道分频器的性质造成的。

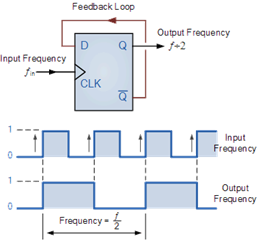

通过将 Q'反馈回 D 触发器、频率得到时钟除以2、但取决于 D 的初始值、输出 Q 是否相对于时钟取反。

问题3:您能否简单介绍一下您的通道分频器是如何工作的? 如果符合我们的想法、那么输出只能有两种形式和180°失调电压。 我们是否可以控制输入、以便在重新淋浴后始终获得类似的结果?

绿色路径:

问题4:为什么将 CHDIV 设置为1 (因此通道分频器= 4)不需要任何同步功能?