主题中讨论的其他器件: LMX2492EVM

我们将 LMX2491与24GHz 雷达前端结合使用、该前端具有16分频的输出、用于 FMCW 雷达。 为此、我们需要 PLL 芯片本身的斜坡/线性调频脉冲特性。 我现已针对 CW 优化了环路滤波器、以便在相位噪声和杂散抑制之间实现折衷、但当切换到30M 斜坡时、我可以清楚地看到前端的 TX 信号中存在一些不连续的情况。

下面是 PLL 仿真:

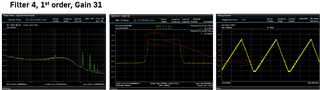

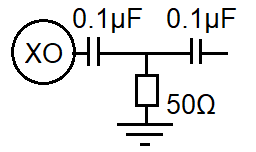

下面是我用于 TICS 的设置:

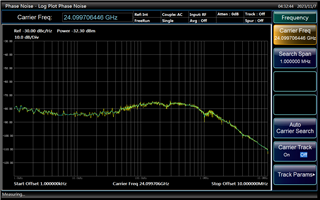

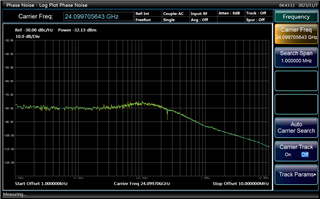

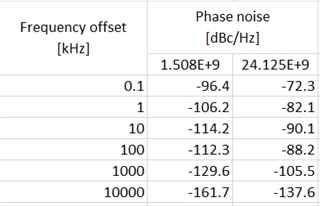

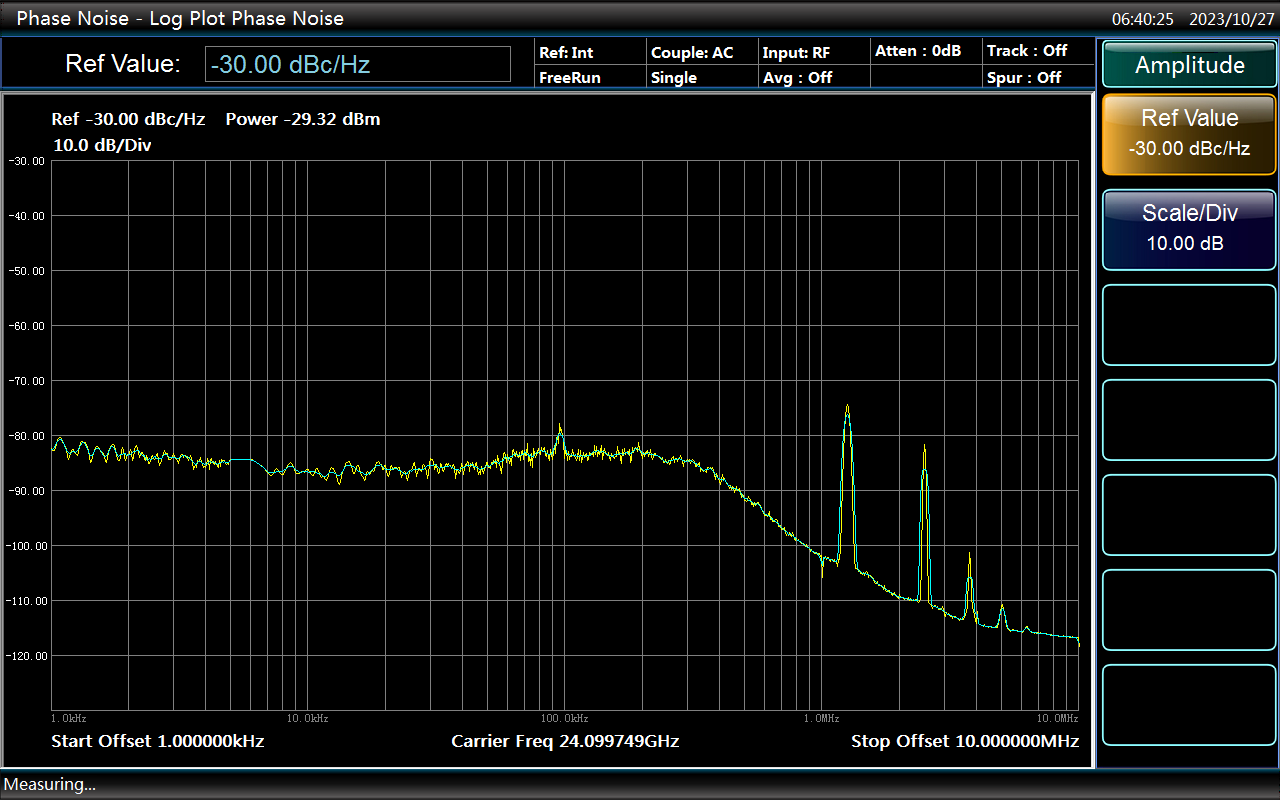

以下是24.1GHz TX 在 CW 模式下的相位噪声图:

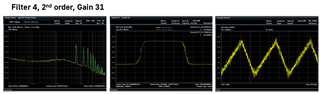

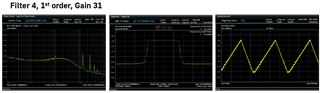

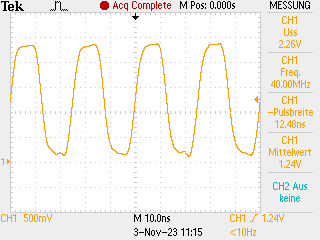

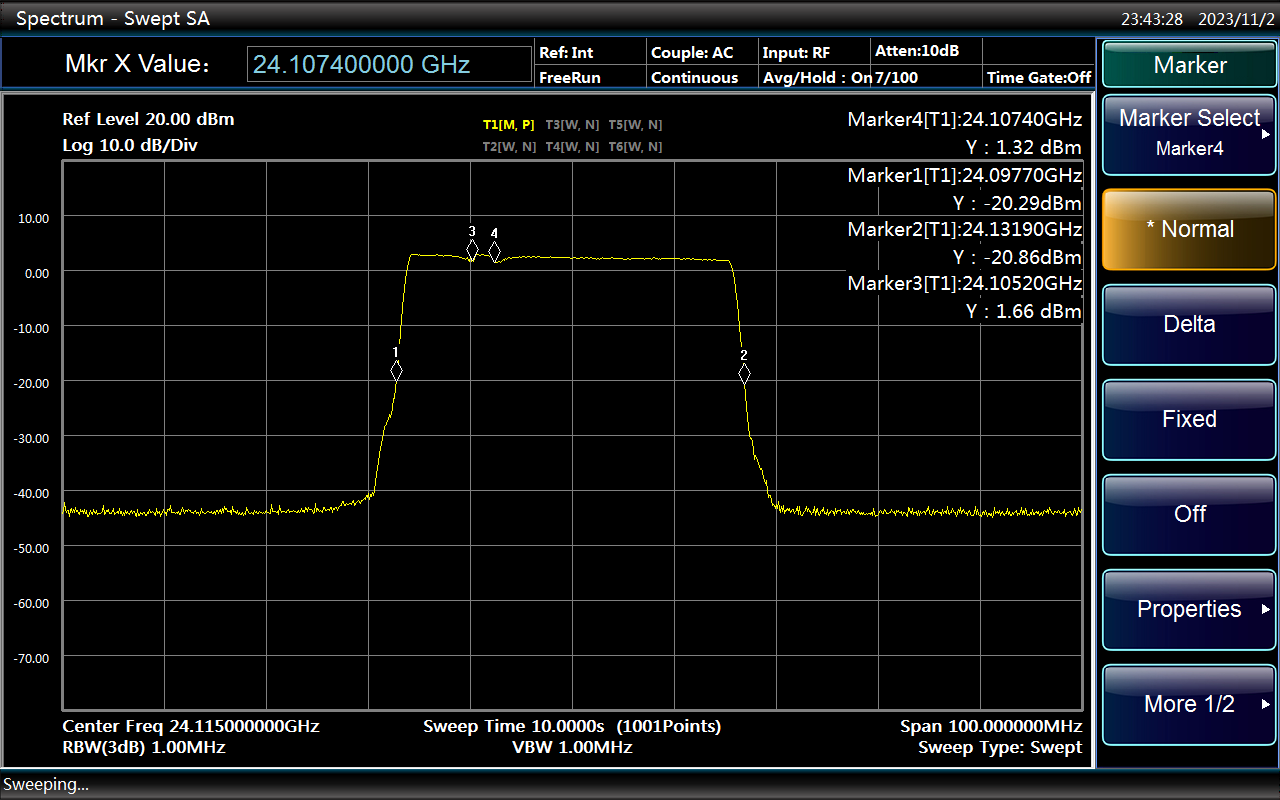

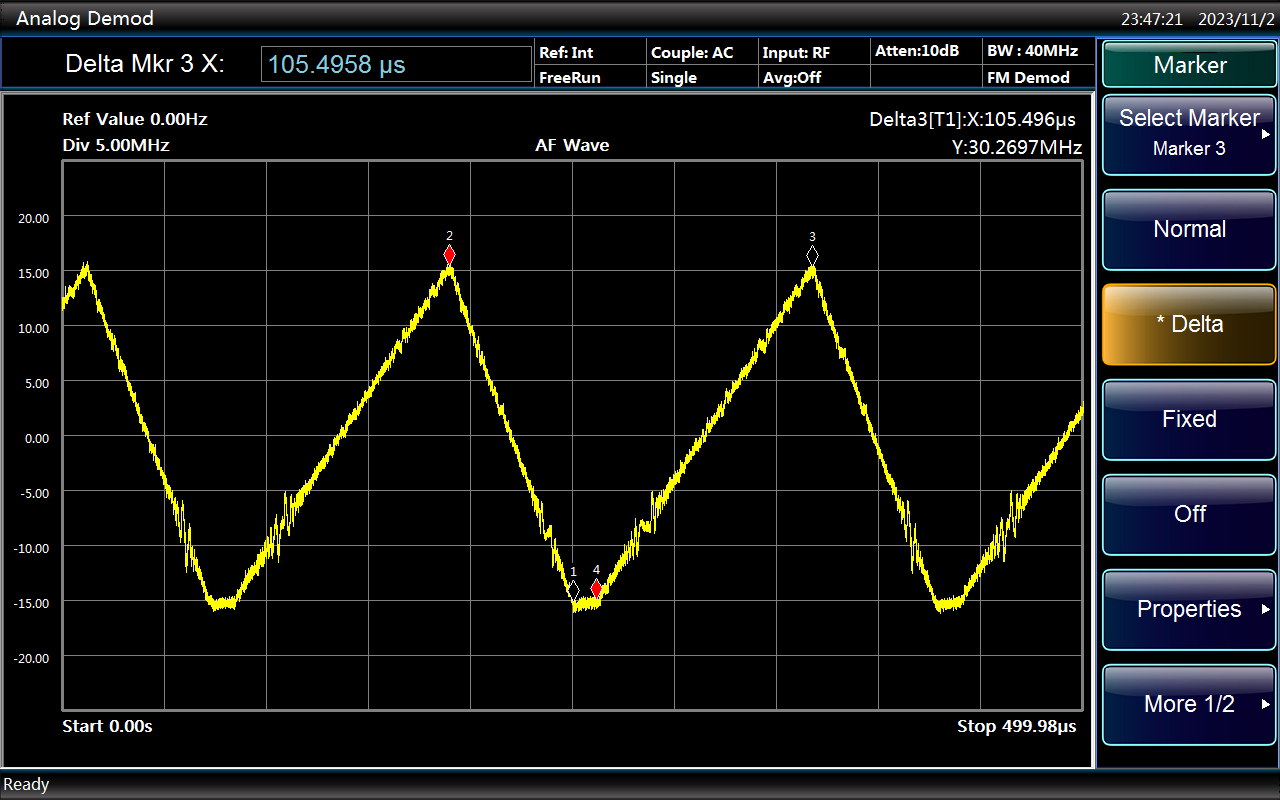

这是随时间测量的 TX 功率和针对斜坡的解调测量:

我尝试了不同的设置、并注意到较低的电荷泵增益也会在斜坡本身中产生较少的杂散和噪声。 此外、我尝试使用不同的 FRAC_ORDERS、但在我的设置中只有 ORDER 一个能够正常工作。 我一旦使用阶2或阶3、看起来环路滤波器就会变得不稳定。

有人知道这种行为的原因是什么吗?