您好:

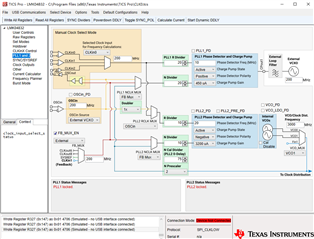

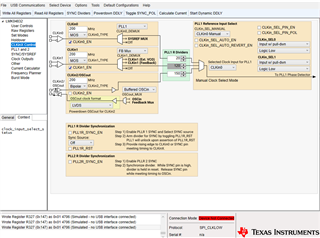

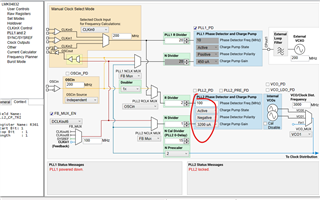

在我的设计中、我使用连接到 CLK_IN0的外部200m 晶体振荡器作为 LMK04832的参考时钟输入。 OSCout 输出200m 作为 FPGA 的工作时钟、确保 FPGA 可在上电和配置 LMK04832后运行。 我将使用 DCLK OUT2作为100M ADC_clk 输出、SDCLK out3作为 SYSREF 输出、并使用 DCLK out8、DCLK out10、DCLK out12、SDCLK out9作为 SDCLK out11作为100M FPGA DDR4控制器输入参考时钟。 我将使用0延迟模式来确保所有输出时钟都具有固定的相位关系。 我已安装 TiCS Pro 和 TI PLLatinum Sim、我将学习使用。

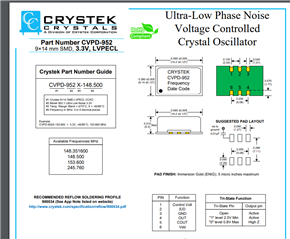

- 如果晶体振荡器性能良好、是否确实需要使用外部 VCXO? 我是否需要使用 CVPD-952作为200M VCXO? 该图像显示的可用频率不包含200m、这是否意味着我无法使用它?

- 我不太清楚零延迟模式的反馈电路需要使用哪个引脚(数据表显示"零延迟反馈可以使用来自 CLKout6、CLKout8、SYSREF 的内部反馈执行、也可以使用进入 FBCLKIN 端口的外部反馈环路(由 FB_MUX 选择)。" 如果选择 内部反馈 ,我不需要 在0延迟模式下进行任何其他外部引脚连接? 如果是这样,我想配置 DCLKout6作为 内部反馈),以及如何使用 PLLatinum Sim 确定环路滤波器的电容和电阻值。 您能否提供使用外部 VCXO 的双环路0延迟模式参考设计的原理图? 如果不需要外部 VCXO、您能否提供单环路0延迟模式的原理图?