主题中讨论的其他器件:LMKDB1120、

您好!

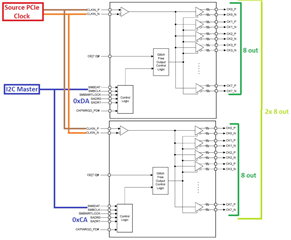

我希望使用两个与两个 CDCDB803组件并联的时钟缓冲器。

输入连接到 PCIe 第4代时钟、

这种设置是否可行?

如何优化此装配体?

最好的正餐

约翰

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Johann:

很抱歉美国假日导致的延迟。 详细了解您的设置后、最好使用具有20个输出的单个 LMKDB1120、并让4个输出悬空、而不是两个 CDCDB803。 使用两个 CDCB803的缺点是需要两个 IC、为布局布线会更多、并且在使用过孔来获得两条输入线时会遇到一些潜在的信号衰减问题。 LMKDB1120也更加理想、因为它仅需要一个 IC、因此您无需担心有两个电源、即输出偏斜和器件间偏斜。

很抱歉耽误你的时间、如果您还有其他问题、请告诉我。

将会