主题中讨论的其他器件: SN74LVC1G17

您好!

我在设计中使用 LMX1204。

通过 SPI 从 FPGA 配置 LMX1204。 我的 FPGA 组电压为3V3、LMX1204在2V5电压下工作。

在数据表中、它告诉 LMX1204可以支持3V3、但 EVAL 原理图已使用2V5电压

是否有人可以确认它是否支持3V3并证明相同?

请尽快回复、我们即将发布制造信息

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我在设计中使用 LMX1204。

通过 SPI 从 FPGA 配置 LMX1204。 我的 FPGA 组电压为3V3、LMX1204在2V5电压下工作。

在数据表中、它告诉 LMX1204可以支持3V3、但 EVAL 原理图已使用2V5电压

是否有人可以确认它是否支持3V3并证明相同?

请尽快回复、我们即将发布制造信息

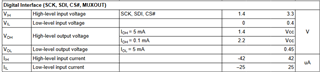

LMX1204可以接受所有输入(SCK、SDI、CS#)上 SPI 引脚的3.3V I/O、如数据表所述:

但请注意、它无法通过 MUXOUT/SDO 引脚产生3.3V 输出。 如果 FPGA 的3.3V I/O 电平禁止使用2.5V 逻辑高电平信号、或者如果 SPI 总线上的负载可能足以降低 MUXOUT 引脚上的输出电压、则可能需要 FPGA 上从 MUXOUT 到3.3V I/O 组的缓冲器。 但在评估板上、我们将2.5V SDO 引脚直接连接到 MSP430、因为在极轻的负载下、我们通常可以满足 MSP430 3.3V I/O 输入要求。

简而言之:如果您希望保护安全、请使用 SN74LVC1G17等输入兼容的3.3V 电平转换器来缓冲 LMX1204 SDO 引脚;LMX1204 SPI 输入具有3.3V 容差。 如果您知道相对于 LMX1204高电平输出电压、FPGA 的输入阈值高电压有裕度、则可以忽略缓冲器、并将 LMX1204 SDO 直接连接到 FPGA。