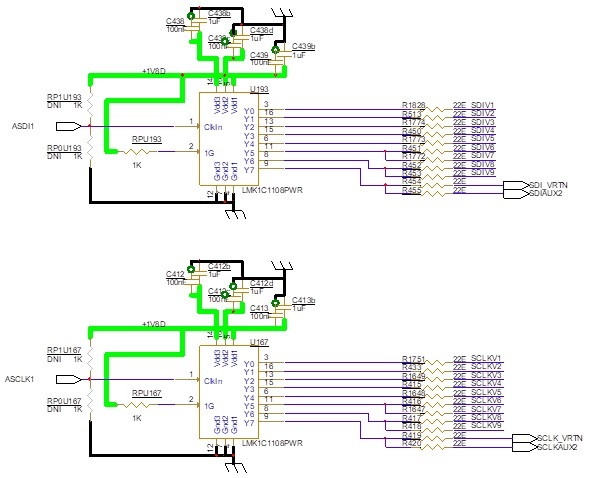

Other Parts Discussed in Thread: LMK1C1108

出于某种原因、在我的电路中、LMK1C1108在使用静态输入时不工作(输入=高电平)。

- 它与一个20MHz 时钟输入(ASCLK1)一同工作。

- 存在阶跃输入(ASDI1)时、输出并不总是从低电平上升到高电平。

在某些情况下、再尝试后、输出变为高电平(输入变为低电平、然后重新设置为高电平)。

- 一方面、DS 显示了一个逻辑电平表、看起来应该支持静态输入。

- 另一方面、DS 以输入信号的周期为单位指定输出启用/禁用时间、这意味着输入不能是静态的。