主题中讨论的其他器件: TLV1117LV

您好、E2E 团队:

请参阅 LMK6C - 12.288MHz BAW 振荡器布局下方的相关指南。

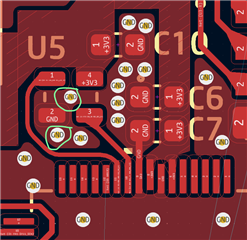

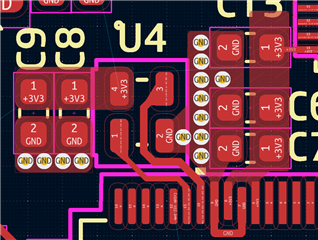

- U4 :LMK6C012288

- C8和 C9 :0.1uF 0603 MLCC

- 引脚3 :振荡器输出- 12.288MHz

- 引脚1 :OE 引脚与 MCU 连接

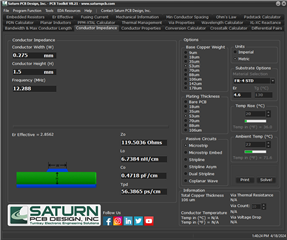

- 2层 PCB 具有60um 铜厚度和1.5mm FR4的

如果可以接受,也请评论:

- LMK6C 的接地引脚与 MCU 的去耦电容器共享、可实现紧凑型布局、均连接到 底层的实心接地。

- 振荡器布线长度为~6mm、宽度为0.275mm、底层为实心接地

- 我们使用了2个采用0603封装的0.1uF MLCC、而不是1uF MLCC

- 电源在输入端具有一个-30dB、高达~1GHz 的铁氧体磁珠 π 型滤波器

- 5V 至3.3V 的 TLV1117LV 用于 π 型滤波器后置

我们是否需要关注反射/去耦 MLCC 值/布局?