主题中讨论的其他器件: LMK04610、 LMK04832

您好!

我正在处理一个使用 Xilinx (AMD) ZCU216开发套件和 CLK104附加卡的项目。 CLK104电路板使用 LMK04828。

我将使用连接到 LMKCLKin0输入的 CLK104板上的 J11 SMA 连接器向 LMKK 芯片提供10MHz 参考信号。 另一个开发套件也将提供与此相同的10MHz 参考。 其目的是在多个电路板上生成一个来自 LMK04828的10MHz 输出时钟、该时钟的频率和相位会相互锁相。 该10MHz 输出将发送到 FPGA、以驱动需要跨多个电路板同步的逻辑。

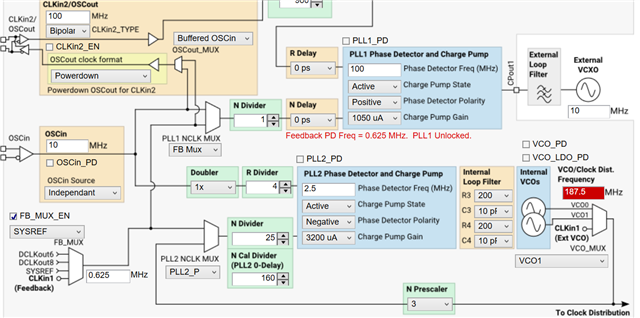

下图显示了我认为我需要如何配置 LMK 芯片。 还包括 TICS 中相应的寄存器转储文件。 目前、我使用的是 SDCLKout11输出、该输出连接到 CLK104板上的 SMA 连接器、可轻松进行监控。

e2e.ti.com/.../CustomHexValues_5F00_ClkIn0_5F00_zerodelay.txt

我想确认我对配置的理解是准确的、并且可以预期行为与我所述的一致性:

- 在这种配置下、如果我期望 CLKin0输入和 SDCLKout11输出都是频率和 和 相位一致?

- 如果我在不同的电路板上以类似的方式配置 LMK 芯片并为其提供等效的10MHz 参考、我是否可以期望所有电路板上的 SDCLKout11输出对齐?

- 我是否需要以某种方式触发同步事件以使相位对齐发生? 我看到在另一个帖子中提到这一点。

如果需要、我可以提供额外的信息。 如果有什么不明确的地方、请告诉我。