主题中讨论的其他器件:LMX2594、

您好!

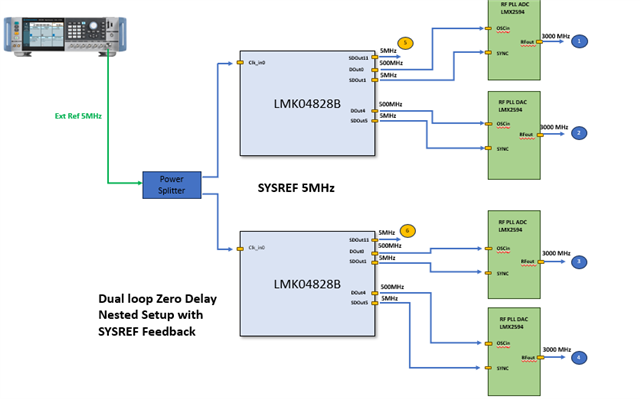

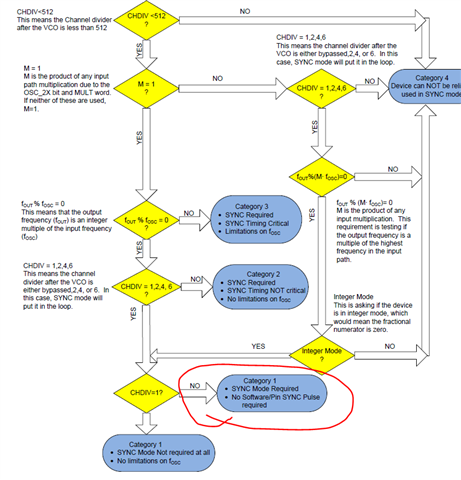

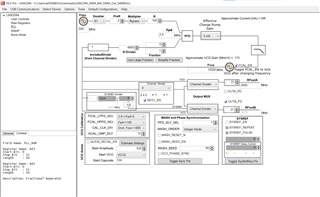

我正在设置一个多板 RFBT 平台、LMK 同步参考案例2b (双环路嵌套0延迟)。

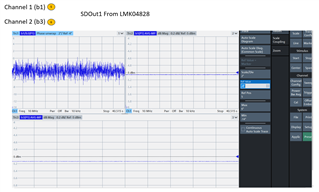

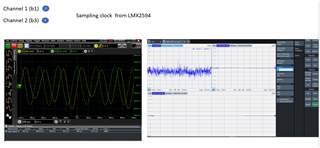

但是、 对于 LMX2594的输出(端口2、端口4)、我们发现相位不同步。

您能仔细检查我的时钟配置吗? 案例2b 是否可以满足我平台的同步要求?

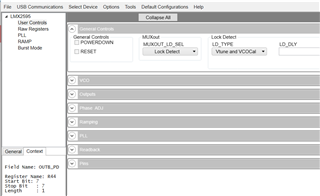

e2e.ti.com/.../LMK_5F00_MTS_5F00_5M_5F00_Bipolar_5F00_AutoRef_5F00_5M_5F00_SYSREF_5F00_500M_5F00_Clocks_5F00_0Delay_5F00_nested_5F00_SYNC.tcse2e.ti.com/.../LMX2594_5F00_500M_5F00_Ref_5F00_500M_5F00_Out_5F00_3000M.tcs