主题中讨论的其他器件: LMK04832

现在、我们正在开发导航有效载荷。

如果我们接收到抖动为+/- 2ns 的10.23MHz 时钟、我们希望使用双 PLL 方案来清理时钟。

我们使用122.76MHz 的输出时钟(12乘以 10.23MHz)。

您能否建议在+/-2ns 范围内清理多少10.23MHz 时钟?

此致

叶在兴

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

现在、我们正在开发导航有效载荷。

如果我们接收到抖动为+/- 2ns 的10.23MHz 时钟、我们希望使用双 PLL 方案来清理时钟。

我们使用122.76MHz 的输出时钟(12乘以 10.23MHz)。

您能否建议在+/-2ns 范围内清理多少10.23MHz 时钟?

此致

叶在兴

宰兴市

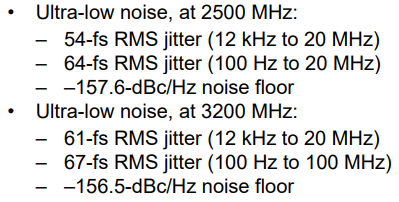

在双环路模式中、输出抖动实际上并不取决于输入抖动、因为相位取自输入信号。 相反、输出抖动主要来自 PLL2 VCO。 数据表给出了这些预期输出抖动示例。

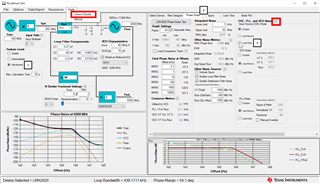

由于您必须从 GHz 级 VCO 频率进行分频、因此会从分频器产生一些额外的噪声。 在使用 PLLatinumSim 进行快速仿真时、我们的 PLL 仿真工具显示、您可能需要~ 113fs 的输出。

此致、

会的

宰兴市

此致、

会的

你好、 在香

PLLatinum Sim 是一款非常好的工具、可以使用和模拟您的数据以及 LMK04832-SP 清理您的数据的工作量。 请注意、我们使用的 是一个非常好的 VCXO、这是将用于清理脏参考的主要组件。

您的意思是输入的相位是输入频率吗?

不对、这意味着时钟的物理相位。 换言之、它与频率无关、它是时钟沿随时间变化的位置。 使用的是在 PLL 的输入信号和 VCXO 的输出之间实现锁相。 这意味着输入信号在与 VCXO 的输出变高的完全同时变为高电平。

我是否需要使用非常简洁的外部 VCXO? 外部 VCXO 的抖动是否与 PLL2的输入抖动直接相关?[/QUOT]这是相对的、但一般而言、您是相对的。 如果您有一个很脏的参考值(3ns 就是这种情况)、则 VCXO 越好、新的相位噪声曲线就越好、因此馈送到第二个 PLL 的输出就越清晰。 您可以在上面链接的 PLLatinum Sim 工具中模拟您需要的 VCXO 的质量。

如果您有新的相位噪声曲线(抖动是相位噪声曲线的积分)、您可以将其视为 VCXO 输出的抖动、因此 PLL2的输入抖动就是所选 VCXO 的相位噪声曲线。 这有道理吗? 我建议您浏览一下 我的一位同事写的有关 PLL 理论的书的 PDF 版本。 您可以在第27章中详细了解抖动以及 PLL 如何清除抖动。

此外、 这 组视频进一步详细介绍了 PLL 以及它们如何清除相位噪声曲线。

[报价 userid="539691" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1345338/lmk04832-sp-lmk04832-sp/5133044 #5133044"]忽略了我的仿真中 PLL2的输入抖动。 我是否需要考虑 VCXO 的抖动? [报价]正如我在上文所解释的、这是不能忽视的。

您能否推荐使用外部 VCXO 输出122.76MHz?上面链接的 VCXO 可以有多种频率、我会前往 Crystek 在122.76MHz 获取 VCXO。

希望这对您有所帮助、

祝您好运、

Andrea

[/quote]

您好、 Adrea

非常感谢您提供的客气答案。

我是否知道可以使用 PLLatinum Sim 使用的方法来模拟双 PLL?

我只能在 PLLatinum Sim 上看到单个 PLL。

我想知道是否输出外部 VCXO 的相位噪声、或者内部环路滤波器是否 可以降低其相位噪声(或抖动)。

该环路滤波器可以在多大程度上减少外部 VCXO 的相位噪声?

此致

Yeaeheung Yeom

您好 Jaeheung:

您必须首先对第一个 PLL 进行仿真、保存该波形、然后在仿真第二个 PLL 时输入该波形。 但是、通过联系您的第二个问题、 PLLatinum Sim 已经考虑将 VCXO 输入到第二个 PLL 中、因此您可以对第二个 PLL 进行分析。 请注意、假设您使用的 VCXO 与我之前附加的相位噪声曲线相同或更好。

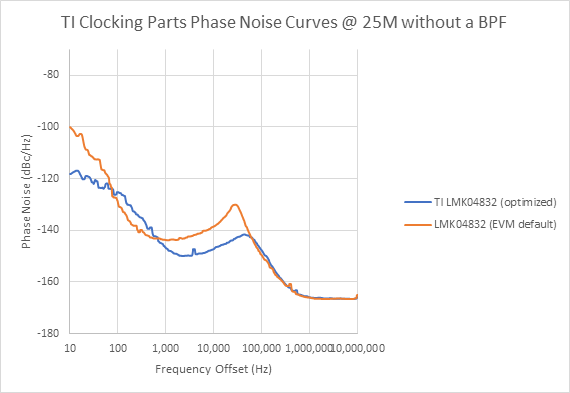

环路滤波器可以显著降低相位噪声、以下是在最大程度地提高环路滤波器的相位噪声并尽可能增加相位检测器频率的示例(请注意、较高的相位检测器频率/较低的 N 分频器值会产生更好的相位噪声)。

此致!

Andrea

你好、 在香

只是想知道、您是否曾尝试过使用 PLLatinum Sim 来查看相位噪声曲线对任一 PLL 的影响? 在该工具中输入 OSCin/CLKIN 并查看结果可以为您澄清几个问题。

通过单个 PLL 可以提高多少输入抖动?

使用 VCXO (或 LMK04832-SP EVM 中的 PLL1)可以显著改善输入抖动。 您是否已尝试向 LMK04832-SP EVM 的 PLL1输入脏信号并查看结果?

[报价 userid="539691" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1345338/lmk04832-sp-lmk04832-sp/5183597 #5183597"]此外、 来自 双 PLL 的输出时钟是否与双 PLL 的输入时钟抖动无关?[/QUOT]PLL1的输出是 PLL2的输入、因此它们是直接相关的。 我回答了上面的问题、请告诉我答案的确切内容不清楚、我可以确保与您一起澄清这些问题!

此致!

Andrea

您好、Adrea

但是、感谢您的回答、我没有得到所需的答案。

我的问题如下:

1) 1)请提供所需的抖动、如"单 PLL"、而不是双 PLL 的 OSCin 数据表中所示的压摆率(0.5V/0.5ns)

2)对于"双 PLL"、 可以改善多少输入抖动、还是与输出时钟的抖动无关?

3) 3)我可以将输入抖动作为仿真条件放在 PLLatinum Sim 中吗?

4) 4)请展示如何 运行双 PLL 仿真

此致

在兴市

Jai-Hung,

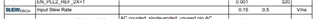

[报价 userid="539691" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1345338/lmk04832-sp-lmk04832-sp/5186057 #5186057"]1)请提供所需抖动、如数据表中关于 OSCin 的"单 PLL"、而非双 PLL的压摆率(0.5V/0.5ns)对于 OSCin 输入、这是所需的压摆率、根据数据表:

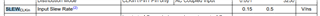

对于 CLKIN 输入、这是数据表所需的压摆率:

换句话说、LMK04832-SP 的任何输入的压摆率要求都需要高于0.15V/ns、并且预期的典型值为0.5V/ns。

[报价 userid="539691" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1345338/lmk04832-sp-lmk04832-sp/5186057 #5186057"]2)对于"双 PLL"、 输入抖动可以提高多少、或者它与输出时钟的抖动无关?[/QUOT]同样、这取决于您使用的 VCXO。 如果您使用良好的 VCXO、例如我在上文 Crystek 推荐的 VCXO、则从输出的输入到输出的抖动可以显著改善。 确切的数字只能通过使用 LMK04832-SPEVM-CVAL 板或使用 PLLatinum SIM 找到。 如果使用 PLLatinum Sim、则需要为工具提供输入相位噪声曲线值、以便它可以估算抖动改善的程度。

[报价 userid="539691" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1345338/lmk04832-sp-lmk04832-sp/5186057 #5186057"]3)我能否将输入抖动作为仿真条件放到 PLLatinum Sim 中? [报价]有

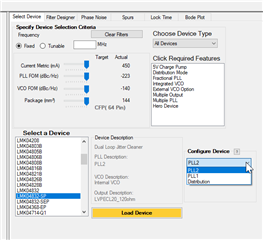

[报价 userid="539691" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1345338/lmk04832-sp-lmk04832-sp/5186057 #5186057"]4)请演示如何 运行双 PLL 模拟1) 1)进行 PLL1仿真。 选择 LMK04832-SP 作为器件、然后选择 PLL1 (忽略下面 pciture 中 PLL2的选择):

您需要通过点击"Load Data"来输入所用参考信号的相位噪声数据、如下所示。 请注意、我突出显示了在哪里可以找到用户指南以及在哪里可以找到"?" 它将提供更多的帮助和指导:

产生的相位噪声曲线仿真(GUI 的左下角)将假设您使用的是 Crystek VCXO、例如 LMK04832-SPEVM-CVAL 上的 VCXO。

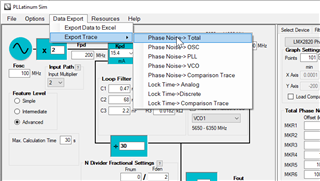

2) 2)在获得仿真(GUI 的左下角)后、您需要导出该数据:

3) 3)然后、返回到"选择器件"页面、选择 PLL2:

...并将导出的数据重新加载到 PLLatinum Sim 中、如步骤2所述。 第二步之后得到的相位噪声曲线将是您的估算值。

以下是 PLLatinum Sim 将接受的.txt 示例(左列是频率偏移、x 轴是、右列是相位噪声值、y 轴):

e2e.ti.com/.../Example_5F00_PLLatinumSIm.txt

此致!

Andrea

你好、Andrea

感谢您快速回答。

1) 1) 除了 数据表中给出的压摆率之外、您能否为单个 PLL 提供输入时钟的抖动?

2、3)我们考虑+/-2ns 的抖动。 如何将输入抖动反映到 PLLatinum Sim 中?

如您所示、 PLLatinum Sim 接受相位噪声曲线而不是抖动。

4) 4)对于相位噪声曲线、频率范围是多少?

我知道相位噪声是从12kHz 到20MHz 或从100Hz 到100MHz 计算得出的。

此致

叶在兴

这取决于您所使用的输入信号、因此我不能向您呈现。 这取决于您要向 LMK04832馈送的信号。

我们考虑+/-2ns 的抖动。 如何将输入抖动反映到 PLLatinum Sim 中?[/QUOT]我在上面附加了一个示例.txt 文件。 基本上、您应该在 x 轴上放置频率偏移、在 y 轴上放置相位噪声值。 请打开上面随附的文件、让我知道您从我的解释中不明白的内容:

[quotaote userid="539691" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1345338/lmk04832-sp-lmk04832-sp/5188436 #5188436]接受相位噪声曲线。以下是一个示例、PLLatinum Sim 将接受作为输入(左列是频率偏移、x 轴、右列是相位噪声值、y 轴):抖动是相位噪声曲线的积分。 它们是相关的、因此需要使用相位噪声曲线来获得抖动。 我建议观看我上面链接的一些视频、以便更好地理解这种关系。

[报价 userid="539691" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1345338/lmk04832-sp-lmk04832-sp/5188436 #5188436"]4)对于相位噪声曲线、频率范围是什么?

我知道相位噪声的计算方法是从12kHz 到20MHz 或者从100Hz 到100MHz。[/报价]这取决于您的系统。 该范围就是您在相位噪声曲线上用于获取抖动的积分带宽。 大多数 A&D 应用使用100Hz 至100MHz 来查看整个相位噪声曲线、而不仅仅是一部分。 12kHz 至20MHz 是我们在各个行业中看到的典型集成带宽。

此致!

Andrea

[/quote]

你好、在香

不存在可接受的最大抖动。 可以将任意数量的抖动输入到系统中。 只需注意、输入的抖动越多、输出的抖动就越多。

2)如何将输入抖动映射到相位噪声曲线中、因为同一抖动量可生成多条曲线?

积分的输入相位噪声曲线为抖动。 所以、您可以更正不同的曲线会产生相同量的抖动。 我认为映射方法是根据数学关系在相位噪声曲线的特定部分添加更多/更少的面积。 同样、我强烈建议您在提出任何进一步的问题之前、先观看视频并详细了解 PLL 和抖动清除器的工作原理。

顺便说一下、如果您需要更多本地支持、这些联系人就是您的本地联系人:David Park (david.park@ti.com)和 Sua Kim (sua.kim@ti.com)

此致!

Andrea

你好、 叶在兴

上述所有信息均在数据表中提供。 如果可能、在向我们询问这些问题之前、请务必阅读本文档。 您也可以联系上面的人员进行任何基本知识审核。

对于 CLKIN 或 OSCin、我是否必须使用差分正弦波源?

您可以使用任一种(数据表中的第9.1.3节)

输入差分方波时、会发生什么情况?

这话什么意思? 为 LMK04832提供此输入时、在正确构建原理图并正确配置器件的同时、器件将按预期运行。

此外,我可以选择 输出时钟的波形是正弦波还是平方波吗?

否、如第8.1.5.7节所述。 可能的输出类型均为方波输出类型、适用于单端和差分输出。

此致!

Andrea

解决差分正弦波问题。 我想知道 是否 可能有差分方波。

LVDS、LVPECL 和 CML 是差分方波类型。

[报价 userid="539691" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1345338/lmk04832-sp-lmk04832-sp/5243982 #5243982"]最后、产生差分正弦波输出的参考时钟源可使用以下电路驱动 CLKIN 引脚。 注意:信号电平必须符合电气特性中列出的 CLKIN 引脚的要求。这种说法是正确的、4832可以做到这一点。 我将再次与我上面发送的联系人联系、以寻求进一步帮助。