请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK5C33216 工具与软件:

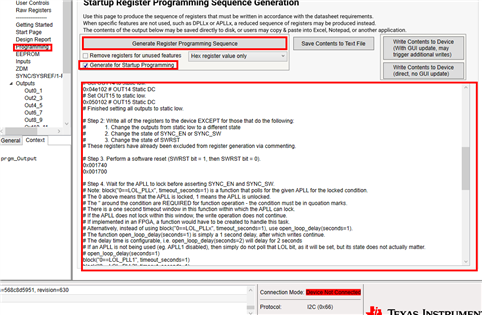

我们正在集成 LMK5C33216、但在理解数据表的意图时遇到一些问题。 我们正在尝试同步两个 SYSREF 输出的计数器、如数据表第57页和58页所述。 我们 通过 R21[6]使用 SYNC_SW、而不是使用硬件 GPIO。 我们最初尝试了以下序列:

- 写入除 SYNC_SW 之外的所有设置寄存器。

- 将 SYNC_SW 置为有效。

- 将 SYNC_SW 置为无效。

最终的行为是 SYSREF 输出似乎已关闭。

我们尝试了 如下第二个序列:

- 将 SYNC_SW 置为有效。

- 写入除 SYNC_SW 之外的所有设置寄存器。

- 将 SYNC_SW 置为无效。

该序列的结果是、两个输出都会启动、并且似乎使上升沿有些同步、但输出的上升沿之间的时间延迟似乎在 上述第2个序列的顺序试验之间变化大约几纳秒。

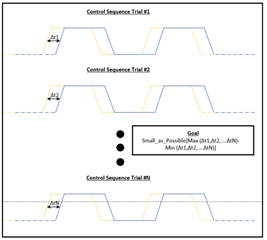

我们的目标是使控制序列的多次顺序试验之间的延迟具有皮秒的变化。 在多次运行建议的控制序列后、是否存在对寄存器写入(使用 SYCNC_SW)顺序的任何了解、该写入会使两个 SYSREF 输出之间的延迟变化最小?

我创建了下面的图形以帮助说明该序列的目标。