主题中讨论的其他器件: LMK04828、 LMK04616

工具与软件:

您好!

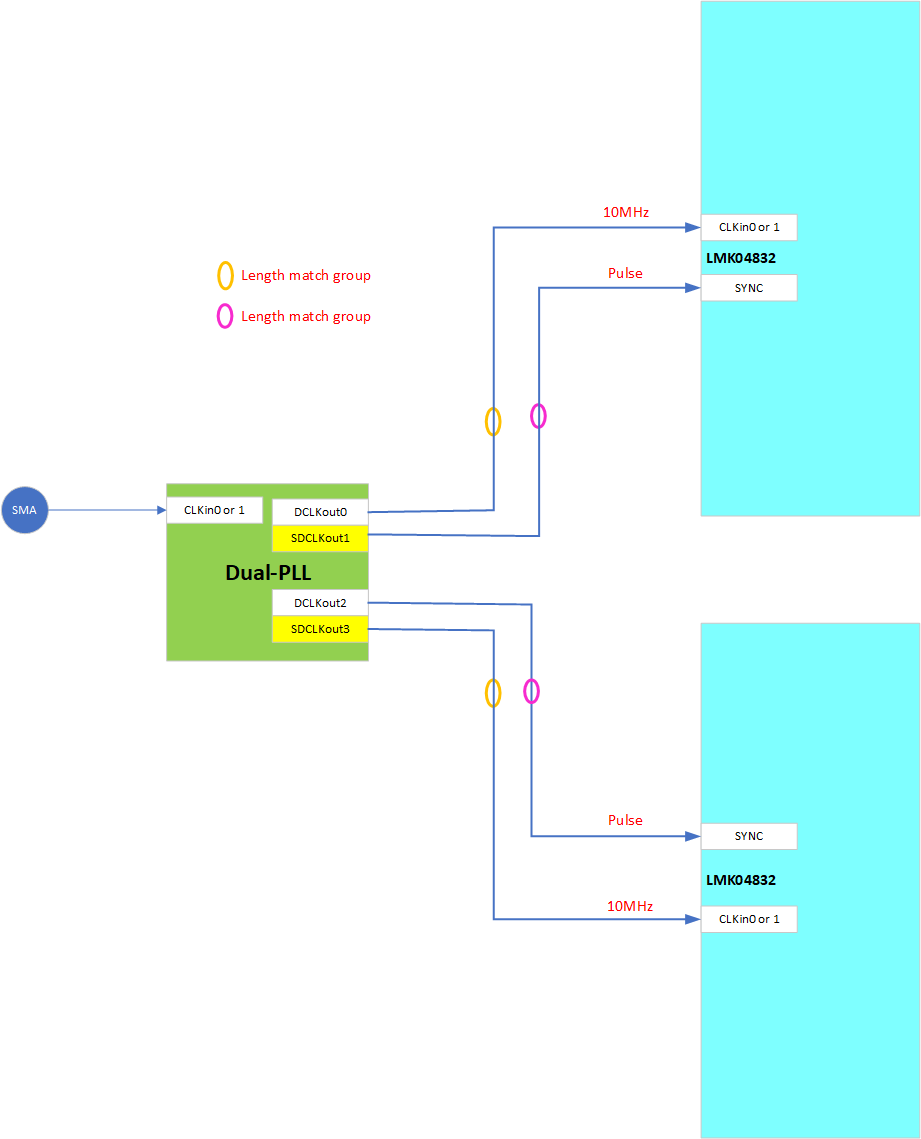

我有一个关于如何为 LMK04832的多芯片提供同步脉冲的问题:

需要将同步脉冲 与 LMK04832的基准时钟同步? 以下两种方案能否获得相同的 同步 精度?

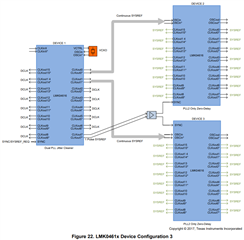

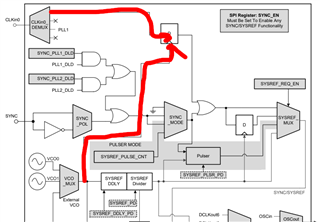

如下图所示、参考时钟和同步脉冲均来自另一个双 PLL、例如 LMK04828或 LMK04832。 在这种情况下、 来自 DUA-PLL 的 SDCLKout 的同步脉冲 与 DCLKout 同步 、DCLKout 是 下一个 LMK04832的 CLKIN 的参考时钟

图1.

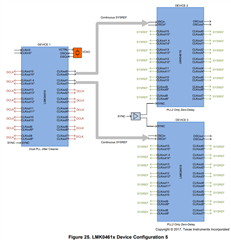

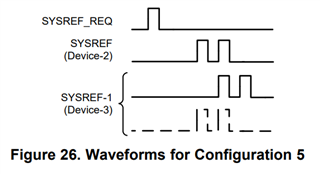

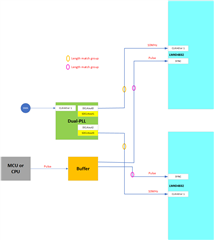

如下图所示、 同步脉冲来自 MCU 或 CPU (通过缓冲器扇出)。 该同步脉冲 完全与下一个 LMK04832的基准时钟异步。

图2.

提前感谢!

此致!

Jason